# **CHARACTERIZATION OF 50nm NMOSFET**

This thesis is presented in partial fulfillment for the award of the Bachelor of Electrical Engineering (Honours)

### UNIVERSITI TEKNOLOGI MARA

MALAYSIA

AZIDDIN BIN AZMAN 2006130613 B. ENG (Hons.) ELECTRICAL Faculty of Electrical Engineering UNIVERSITI TEKNOLOGI MARA MALAYSIA (UiTM) Shah Alam, Selangor Darul Ehsan.

### ACKNOWLEDGEMENT

In the name of ALLAH S.W.T with His Almighty, the Most Beneficent and Merciful, with the deepest gratefulness to Allah who has given me the strength and ability to complete this thesis. I would like to thanks to my friend by providing tool and helping me on my final year project. Without their helped, maybe this project cannot be completed. Thanks to my supervisor, Dr Fuziah Sulaiman for advising and suggest me on finishing my project. Thanks also to the En Ahmad Sabirin for providing me info about project. Also thanks to the Lab Silvaco facility by allowing us to use the instrument and provide the software to us. Special thanks to my parent for giving support and motivation, wish all of you best.

### ABSTRACT

This paper presents a detailed study of characteristic of 50nm MOSFET by using SILVACO TCAD tool. The gate length (*L*) is reducing into 50nm based on conventional 0.3µm NMOSFET. The result of performance between two structures is compared by using Atlas simulation. The analysis is focused on  $I_d$ - $V_g$  and  $I_d$ - $V_d$  characteristic on the two gate length as mentioned. ATHENA and ATLAS in SILVACO TCAD tool was used to construct and analyze the semiconductor device. The result has shown how the drain current increase steadily and improvement on threshold voltage by 50nm NMOS in comparison with 0.3µm technology.

*Keyword*- 50nm NMOS, I<sub>d</sub>-V<sub>g</sub>, I<sub>d</sub>-V<sub>d</sub>, Simulation

### TABLE OF CONTENTS

| DECLARATION           | i   |

|-----------------------|-----|

| ACKNOWLEDGEMENT       | ii  |

| ABSTRACT              | iii |

| TABLE OF CONTENTS     | iv  |

| LIST OF FIGURES       | vii |

| LIST OF TABLES        | ix  |

| LIST OF ABBREVIATIONS | X   |

| CHAPTEI | <b>R DESCRIPTION</b> | PAGE |

|---------|----------------------|------|

|         |                      |      |

## 1 INTRODUCTION

| 1.1 History Background of MOSFET | 2 |

|----------------------------------|---|

| 1.2 Objectives                   | 4 |

| 1.3 Scope of project             | 4 |

| 1.4 Thesis Organization          | 5 |

## 2 LITERATURE REVIEW

| 2.1 Metal Oxide Semiconductor Field |    |

|-------------------------------------|----|

| Effect Transistor (MOSFET)          | 7  |

| 2.2 MOSFET operation                | 8  |

| 2.2.1 The short and long channel of |    |

| MOSFET                              | 9  |

| 2.2.2 Threshold voltage             | 11 |

| 2.2.3 Gate oxide thickness          | 12 |

| 2.3 Fabrication of NMOSFET          | 13 |

#### **CHAPTER 1**

### **INTRODUCTION**

#### **1.1 History Background of MOSFET**

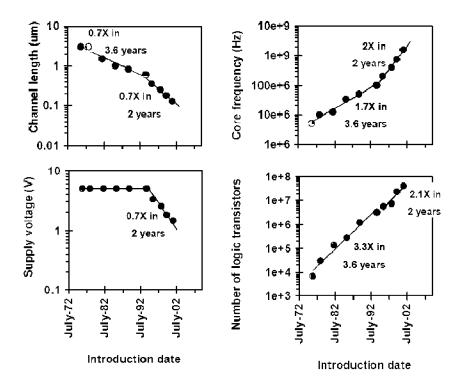

MOS transistor based integrated circuits have transformed the world we live in. It is estimated that there are more than 15 billion silicon semiconductor chips currently in use with an additional 500,000 sold each day [1]. The ever shrinking size of the MOS transistors that result in faster, smaller, and cheaper systems have enabled ubiquitous use of these chips. Among these semiconductor chips, a prevalent component is the high-performance general-purpose microprocessor. Figure 1-1 illustrates the timeline on technology scaling and new high performance microprocessor architecture introductions in the past three decades [3].

Figure 1-1: Timeline on technology scaling and new microprocessor architecture introduction.