# IMPLEMENTATION AND SIMPLIFICATION OF AN OUTPUT SHIFTED CODING MODULATION (OSCM) ON A HIGH SPEED DSP PROCESSOR.

### **BY** :

### ROSLINA MOHAMAD WAN NOR SYAFIZAN WAN MUHAMAD ROSMALINI ABDUL KADIR

**JUN 2009**

## ABSTRACT

Forward error correction (FEC) codes are a subclass of error correcting codes, have become an invaluable tool in 'closing' the link budget of wireless-based digital communications systems. The disadvantage of FEC is the tradeoff between error performance and the decoding complexity resides on the choice of the code constraint length. A solution to this problem was provided by Ungerboeck, who presented a technique which is called Trellis Coded Modulation (TCM). However, there is still a trade-off at work; trellis coded modulation achieves coding gain at the expense of decoder complexity. Due to this problem, a new coded modulation which is a combination of forward error correction codes (convolutional and Viterbi codes) and  $\pi/4$ -shift DQPSK is discussed in this research. The new coded modulation is called as Output Shifted Coding Modulation (OSCM). This algorithm also shows that by using low constraint length convolutional component codes, it can outperform the convolutional codes using Viterbi decoders with much higher constraint lengths. It is capable of reducing the bandwidth expansion by using  $\pi/4$ -shift DQPSK. This is achieved through fine tuning the set of rules for the mapping of coded bits and also with modifying error detection and correction techniques in trellis diagram.

The research work continues with the implementation of digital baseband signal processing with OSCM function on Digital Signal Processor (DSP) Kit TMS320C6711. Single DSP chip is used to implement the baseband processing function due to compactness, low-power consumption and flexibility. C6711 is a member of the high performance DSP family from Texas Instruments (TI) that incorporated the real-time kernel known as DSP/BIOS. The design environment is based on Code Composer Studio IDE (Integrated Development Environment) and the DSP functions are simulated on 150MHz clock C6700 DSP simulator.

## ACKNOWLEDGEMENT

Setinggi-tinggi penghargaan dan ribuan terima kasih diucapkan kepada semua pihak yang terlibat secara langsung dan tidak langsung bagi membolehkan penyelidikan ini disiapkan dengan sempurna.

Diantaranya :

Prof. Dr Titik Khawa Abdul Rahman (Dekan Fakulti Kejuruteraan Elektrik)

Prof. Madya Dr. Habibah Hashim (Pengerusi Pusat Pengajian Komputer)

> En. Nuzli Bin Mohamad Anas (Jurutera MIMOS Bhd)

> > dan

Semua individu yang telah memberikan kerjasama dan sokongan di dalam menjayakan penyelidikan ini

## TABLE OF CONTENTS

| ABSTRACT i                                                       |            |

|------------------------------------------------------------------|------------|

| ACKNOWLEDGEMENT                                                  | ii         |

| TABLE OF CONTENTS                                                | iii        |

| LIST OF FIGURES v                                                |            |

| LIST OF TABLES vi                                                |            |

| LIST OF ABBREVIATIONS                                            | vii        |

| LIST OF NOMENCLATURES                                            | ix         |

| CHAPTER 1: INTRODUCTION TO OUTPUT SHIFTED                        |            |

| MODULATION (OSCM)                                                | 1          |

| 1.1 OSCM Encoder                                                 |            |

| 1.2 Trellis Diagram for OSCM Encoder                             |            |

| 1.3 OSCM Decoder                                                 | 6          |

| 1.3.1 Multilevel Decision Input Method                           | 7          |

| 1.3.2 Soft Decision Input Method                                 | 8          |

| 1.3.3 Modified Viterbi Algorithm                                 |            |

| 1.4 Example of Using OSCM Decoder                                | 8          |

| 1.4.1 Non Corrupted Signal                                       |            |

| 1.4.2 Corrupted Signal with AWGN                                 | <b>1</b> 1 |

| 1.5 Comparison Decoding Results                                  | 13         |

| CHAPTER 2 : IMPLEMENTATION OF AN OSCM ON A DSP PROCI             | ESSOR 15   |

| 2.1 Structure of Firmware for Digital Baseband Signal Processing | 15         |

| 2.1.1 DSPs Starter Kits                                          |            |

| 2.2 Implementation of DBSP Functions                             | 17         |

| 2.3 DBSP Transmitter                                             |            |

| 2.3.1 G.729A Speech Encoder                                      | 19         |

| 2.3.2 Convolutional Interleaver                                  | 20         |

| 2.3.3 OSCM Encoder                                               | 22         |

| 2.4 Looping Connection                                           | 25         |

| 2.5 Baseband Receiver                                            |            |

| 2.5.1 OSCM Decoder                                               |            |

| 2.5.2 Convolutional DeInterleaver                                |            |

| 2.5.3 G.729A Speech Decoder                                      |            |

| 2.6 Experimental Procedure                                       |            |

| 2.7 Conclusion                                                   |            |

| CHAPTER 3 : RESULTS AND DISCUSSIONS                              | 33         |

| 3.1 Analysis on Complexity Performance of OSCM                   | 33         |

| 3.2 Discussion on BER and Complexity Performance of OSCM         |            |

| 3.3 Performance Results of Implementation                        |            |

|                                                                  |            |

## CHAPTER 1: INTRODUCTION TO OUTPUT SHIFTED CODING MODULATION (OSCM)

#### 1.1 OSCM Encoder

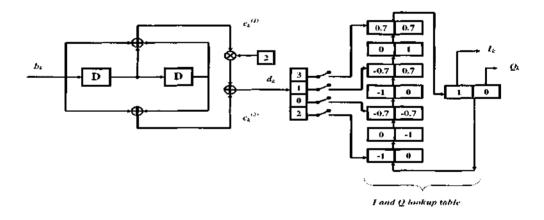

OSCM encoder consists of modified convolutional encoder (CE) and  $\pi/4$ -shift DQPSK modulator as shown in Figure 1.1. This encoder consists of G (7, 5), K=3 CE, which located in the left of the OSCM encoder, while in the right side consist of  $\pi/4$ -shift DQPSK modulator with lookup table systems. OSCM encoder starts with CE operation. The information sequence  $b_k = (b_0, b_1, b_2, ..., b_n)$  enters the encoder one bit at a time. Since the encoder is a linear, two encoder output sequences  $c_k^{(1)} = (c_0^{(1)}, c_1^{(1)}, c_2^{(1)}, ...)$  and  $c_k^{(2)} = (c_0^{(2)}, c_1^{(2)}, c_2^{(2)}, ...)$  can be obtained as the convolution of the input sequence  $b_k$  with the two encoder "impulse responses". The impulse responses are obtained by letting  $b_k = (1 \ 0 \ 0 \ ...)$  and observing the two output sequences.

Figure 1.1 Output shifted coding modulation encoder.

Lets the input bit is defined as

$$\mathbf{b}(\mathbf{D}) = \mathbf{b}_0, \mathbf{b}_1, \mathbf{b}_2, ..., \mathbf{b}_n \tag{1.1}$$

From trellis diagram for G (7, 5), two lookup table are developed which are next state lookup table (Table 1.1) and output lookup table (Table 1.2). From Table 1.1, the possible transition of state can be written as: