# Investigation of Doping Techniques on the Silicon Based Capacitor

A.S. Zoolfakar, A.A. Yaacob, M. Zolkapli, A. Zakaria and M.Z. Abdul Wahab

Abstract— This technical paper investigates the effect of doping techniques, type of dopant species and the plate size on the capacitance density of a silicon based capacitor. The substrate of the silicon wafers are highly doped using either solid source (SS) or spin-on dopant (SOD) method. Experiments are carried out at three different diffusion temperatures, 900°C, 1000°C and 1050°C. Results show that the diffusion by spin-on dopant gives a higher capacitance density compared to diffusion by solid source while larger plate size leads to a larger capacitance value. In addition, the experiment also shows that n-type wafer heavily doped with phosphorus exhibits a higher capacitance density.

Index Terms— solid source, spin-on dopant, capacitance density, segregation, pile-up, heavily doped bulk substrate

## I. INTRODUCTION

In general, capacitors have a dielectric that is sandwiched between a pair of parallel electrodes, and function to store electricity. The characteristics of the capacitors largely vary depending on the type of dielectrics used. Capacitance has been found to be inversely proportional to the thickness of the dielectric material, thus thin film capacitors are generally seen as a preferable means to achieve high performance [1]. As the electronic circuits are being miniaturized to an increasing degree as a

Manuscript received May 14, 2010.

Ahmad Sabirin Zoolfakar, Ahmad Akmalhakim Yaacob and Maizatul Zolkapli are with the Faculty of Electrical Engineering, Universiti Teknologi MARA Malaysia, Shah Alam, Selangor, 40450, Malaysia (email:ahmad074@salam.uitm.edu.my).

Azlan Zakaria is with the Faculty of Applied Science, UiTM and Mohd Zahrin Abdul Wahab is currently working with MIMOS Berhad. result of advances in the integrated circuit technologies, the miniaturization of capacitors that are indispensable in the integrated circuits as circuit elements is also becoming especially significant [2]. To achieve large-capacity capacitors, the thickness of an insulating layer interposed between the capacitor electrodes should be reduced. The silicon based capacitor in this experiment resembles the concept of a parallel plate capacitor using silicon dioxide as the dielectric layer [3].

The main objective in this paper is to study the effect of different doping methods such as solid source (SS) and spin-on dopant (SOD), type of dopant species used and the capacitor plate size in relation to the capacitance density. These parameters are of interest because of the effect on the capacitance density can be seen and investigated when the values are varied. Based on previous studies, it is known that different doping concentration and impurity types introduced into the silicon could affect the thickness of the oxide layer grown during the thermal oxidation process. To strengthen the reason for choosing the variables, the capacitance (1), and the capacitance density (3) equation of a parallel plate capacitor are referred. Parameters such as the separation distance between the plates, d is related to the oxide dielectric thickness and the plate area, A is related to the size of the capacitor. The diffusion temperatures used for the diffusion process of phosphorus and boron impurities in the silicon substrate are 900°C, 1000°C and 1050°C.

The silicon substrates are heavily doped with the same dopant type as the original wafer type to increase the majority carrier concentration in the substrate regardless of the doping method used. Hence, the contribution of the minority carriers in the substrate has a minimum effect on the capacitance density [4].

## II. METHODOLOGY

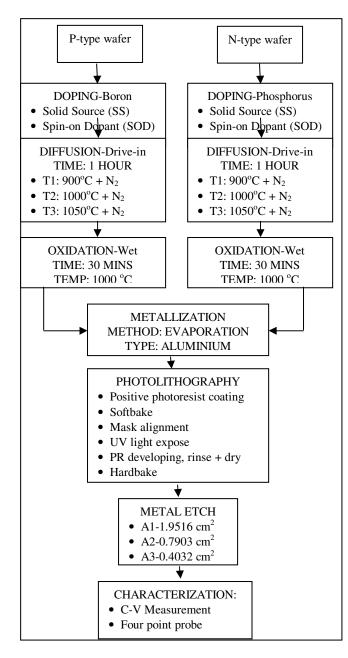

The methods and processes conducted throughout the experiment are clearly stated in Fig. 1. Four-inch silicon wafers with <100> orientation are used in the experiment. In order to observe the difference in characteristics of the p-type and n-type capacitors, the initial fabrication step is divided into two groups. Throughout the fabrication, the samples undergo diffusion, oxidation and also metallization processes.

Firstly, the wafers are cleaned using the wet cleaning procedure to remove native oxide and other contaminants. The wafers are immersed in the Buffered Oxide Etch (BOE) solution which is a mixture of hydrogen fluoride (HF) and ammonium fluoride (NH<sub>4</sub>F), then rinsing it with de-ionized water (DIW).

Regardless of the doping methods and dopant types used, a flow of  $N_2$  gas of 10 standard liter per minute (slm) is introduced in the diffusion furnace in order to prevent impurities from depositing on the silicon wafer. Nitrogen gas carries unwanted impurities away from the furnace. During the metallization process, a thin layer of Aluminum is deposited on the grown oxide layer using evaporation in low pressure method. This process is carried out in the Modu-Lab PVD.

Three different sizes of capacitors which values are P1=1.9516 cm<sup>2</sup>, P2= 0.7903 cm<sup>2</sup>, P3= 0.4032 cm<sup>2</sup> are fabricated to study the effect of different plate sizes on the capacitance value. The mask used in this experiment is designed using TurboCAD Designer15 software.Positive type photoresist is used in the experiment. The resist is deposited on the aluminum by using the Laurell Model WS-400E single wafer spin processor. The spin speed is set to 1500 rpm for 30 s. The samples are then placed on the hot plate for softbake process at the temperature of 100 °C for 5 mins. Then, the sample is exposed under UV light for 50 s. Next, the photoresist is developed by dipping the sample into the resist developer. The final lithography process is to hardbake the sample for 7 mins at the temperature of 110°C.

Fig. 1: Flowchart of the experimental procedure

In order to obtain the desired capacitor size, the aluminum layer is then etched by submerging the samples into the aluminum etch solution at 65 °C for 90 mins. The sample in the aluminum etch solution can be agitated to obtain a more uniform etching.

Low frequency CV measurement is conducted on the samples to obtain the CV plot in order to study the electrical properties of the capacitor. This test is performed using the Keithley 595 Quasistatic CV meter and the Modu-Lab Benchtop CV software. Voltages between -3 V to +3 V are swept on the metal gate of the capacitors. The data of capacitance at certain voltages is then analyzed using Microsoft Office Excel 2007.

#### III. RESULTS AND DISCUSSION

In this experiment, all the values of capacitance density are taken when the voltage applied is +1 V. Upon using MathCAD for simulating a MOS capacitor with similar characteristics of the fabricated capacitors, it has been found that the CV plot for all the samples shared a similar trait where all of the capacitors fabricated operate in their accumulation phase at +1V.

# A. Effects of Doping Techniques

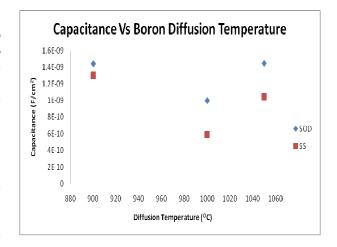

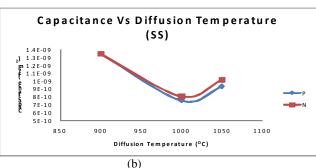

The capacitance against diffusion temperature is plotted in Fig. 2, to study the effects of different doping techniques used to diffuse boron and phosphorus on the capacitance density.

Equation 1 and 2 are the capacitance equation, C of a parallel-plate capacitor and equation 3 is the capacitance density.

$$C = \varepsilon_r \varepsilon_0 \frac{A}{d}, \tag{1}$$

$$C = \frac{\mathrm{d}q}{\mathrm{d}v} \tag{2}$$

$$\frac{C}{A} = \frac{\varepsilon_r \varepsilon_0}{\overline{d}} \tag{3}$$

Fig. 2: Capacitance against diffusion temperature (a) Si doped with boron (b) Si doped with phosphorus

From Fig. 2 (a) and (b), it can be seen that the capacitance density of the SOD method is higher compared to the capacitance density of the capacitors fabricated using the SS method. This phenomenon can be explained by the fact that diffusion by SOD method introduces a lower impurity concentration in the silicon substrate compared to diffusion by SS.

It is also found that the oxidation rate increases with increasing dopant concentration [5]. This means during thermal oxidation, the oxide thickness over the heavily doped regions may be greater than over the lightly doped region. From the findings, it can be said that the SOD method yields a thin oxide thickness hence results in larger capacitance density.

Based on equation (1) and (3), it can be deduced that any changes to the value of distance between the capacitor plate, *d* will in turn affect

the capacitance, C. The main focus upon discussing this factor is the difference in the oxide thickness grown during the wet oxidation process. Taking the oxide thickness as the separation distance between the plates, d it is shown that the value of capacitance is inversely proportional to d.

Reasons for the difference of impurity concentration introduced in the substrate between the two diffusion methods are explained in the next subsections.

# i. Spin-On Dopant (SOD)

Silicate Spin-On Glass (SOG) may be doped with phosphorus or other dopants. A doped SOG is often called Spin-On Dopant (SOD) when it is used as a diffusion source. The viscosity of the silicate SOG solution is fairly low. As a result, the obtained layer by each spin is very thin. The planarity is generally poor and it normally requires multiple spins to achieve good planarity [6].

Furthermore, diffusion of SOG doped with boron or phosphorus could make the film hygroscopic and when react with water at room temperature, will lead to the formation of volatile compounds at the diffusion temperature. In the consideration of boron, this gives rise to variation in the amount of B<sub>2</sub>O<sub>3</sub> reacted with silicon. Thus great care must be taken to keep the deposited wafer from coming in contact with moisture if reproducible diffusions are to be achieved [6].

In addition, one of the factors that control the deposition process is the diffusivity of the impurity atoms [7]. In terms of the diffusion rate, it is known that matters in gaseous form would diffuse much faster than matters in the form of liquids or solids. Therefore, this could also be related to the reason why the diffusion of impurity atoms into the substrate using the SOD method is slower.

# ii. Solid Source (SS)

The SS doping method introduces a more purely doped impurity species in the semiconductor substrate. During the diffusion process, a small flow of  $N_2$  is used to prevent back streaming of airborne contaminants into the diffusion tube and due to this reason, the impurity concentration on the surface of the substrate will be higher because of the uninterrupted flow of impurities [7].

In terms of p-type doping, high concentration of boron can be transported from the BN disc using a process termed hydrogen injection. Hydrogen is streamed to the discs to form a HBO<sub>2</sub> vapor which has a high vapor pressure, therefore significant surface concentrations of boron on the Si can be achieved with this technique [7].

## B. Effects of Impurity Types

The next factor that will be discussed is the effect of dopant species type used to dope the bulk substrate. It is mentioned in the procedure that the n-type wafer is heavily doped with phosphorus while the p-type wafer is heavily doped with boron.

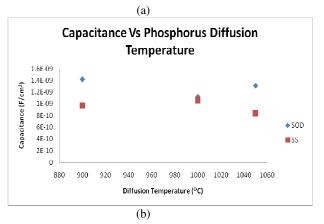

Fig. 3: (a) Capacitance against SOD diffusion temperature for boron/phosphorus doped wafer, (b) Capacitance against SS diffusion temperature for boron/phosphorus doped wafer.

As previously discussed, the thickness of the oxide layer grown is strongly linked with the impurity concentration in the silicon substrate. The overall opinion on the mechanism of the oxide growth is that it occurs at the interface of the Si-SiO<sub>2</sub> which initial reaction rate is limited by the interface, resulting in a linear growth relation. As the oxide thickness progresses, the diffusion-limited process of the oxygen traversing

through the oxide limits the growth rate and the reaction becomes inversely dependent on the oxide thickness. This results in a parabolic growth rate [8].

During the thermal oxidation process, dopants redistribute between the growing oxide and silicon as the Si-SiO<sub>2</sub> boundary moves into the silicon bulk and can cause considerable changes in the impurity in silicon near its surface [9].

The physical "tendency" of dopants to diffuse either in oxide or silicon is quantified by the segregation coefficient, m.

# m = <u>Equilibrium concentration of impurity in Si</u> Equilibrium concentration of impurity in SiO2 (4)

Fig. 3 (a) and (b) depicts the p-type substrate doped with boron exhibiting an overall lower capacitance density compared to the n-type substrate doped with phosphorus at higher diffusion temperature. This result will be discussed in terms of changes occurring on the thickness of the oxide dielectric layer. In turn, relating to variations on the distance between the capacitor plate, d in (1) and (3). Since the thermal oxidation process in this experiment is conducted at 1000°C with the presence of H<sub>2</sub>O, it is known that the main mechanism for the oxide growth at this temperature is related to the parabolic growth rate [9]. In the discussions below, it is important to keep in mind that at higher diffusion temperature, the impurity concentration of boron or phosphorus at the Si-SiO2 interface will also increase.

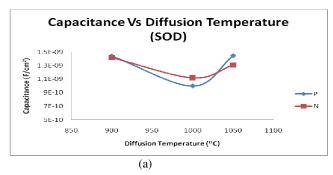

The results also shows a "V" shaped relation between each of the three points. This relation can be explained by referring to the maximum solid solubility of the impurities that can be put into the wafer. From the graph of concentration against diffusion temperature for the solid solubility of impurities in silicon, it can be seen that the solubility of impurities including boron phosphorus initially increases and with temperature (900°C) and then begins to decrease (1020°C) as the crystal melting temperature is approached. This is known as retrograde solubility [7]. It is previously found that the melting temperature for silicon in the form of solid is approximately at 1414°C.

## i. Phosphorus Doped Silicon

Since phosphorus has a high segregation coefficient of approximately ~10, it has the tendency to "pile-up" at the silicon surface during thermal oxidation, while their concentration in the oxide remains low [7]. Thus, making the oxide layer more difficult to move into the silicon substrate and limiting the growth of oxide dielectric layer.

At 1000°C, a high bulk concentration of phosphorus causes little change in oxidation rates which means higher capacitance density. This is consistant with the findings of Haas and Gray (1975) [8]. Due to the "pile-up" effect, the oxide produced will be essentially SiO<sub>2</sub> and subsequent oxygen diffusion through it will not be significantly affected.

In Fig. 3 (a), it can be seen that at the diffusion temperature of 1050°C, the capacitance density of the boron-doped silicon is higher compared to the phosphorus-doped silicon. This slight deviation might have been caused by the doping method used. The deposition of the boron spin-on dopant might have been poor and in turn leads to a lower impurity concentration in the substrate.

## ii. Boron Doped Silicon

The cause of oxidation rate dependence on boron is different from that of phosphorus. At 1000°C, boron with the segregation coefficient of ~0.3, tends to segregate into and remains in the silicon dioxide during thermal oxidation. Hence, the bond structure of the silicon dioxide weakens due to the large boron concentration. This in turn, allows both O<sub>2</sub> and H<sub>2</sub>O to enter the silicon dioxide more easily and also to diffuse through it more rapidly, thereby leading to enhanced oxide growth [7] which in turn, obtaining a lower value of capacitance.

The decrease in capacitance value from the temperature of 900°C to 1000°C is shown in Fig. 3 (a) and (b). The main reason for the decrease in capacitance value is because the oxide thickness in both boron-doped and also phosphorus-doped silicon has increased. The result in Fig. 4 (b) agrees with the observation made by Deal and Sklar (1965) which shows that at the oxidation temperature of 1000°C, substrates highly doped with boron will obtain a higher oxidation rate compared with high boron-doped substrate [10].

This is because there will be more boron impurities available in the oxide layer due to the property of segregation. As explained before, the structure of the silicon dioxide will have more tendencies to be weakened.

#### C. EFFECTS OF IMPURITY TYPES

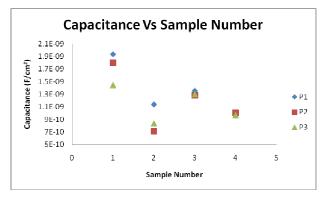

The final characteristic studied is the effect of the capacitor sizes on the capacitance. Three different sizes of capacitor are fabricated.

From Fig. 4, it can be interpreted that the largest capacitance density is given by the largest capacitor size, P1. Reason for this matter is best explained by the well-known equation for capacitance (1) where, A is the area of the conducting plates between the dielectric and is directly proportional to the capacitance density.

Fig. 4: Capacitance value against sample number P1= 1.9516cm<sup>2</sup>, P2= 0.7903cm<sup>2</sup>, P3= 0.4032cm<sup>2</sup> S1= P-type SOD, S2= N-type SOD, S3 = P-type SS S4= N-type SS

Analogous to the operation of a parallel plate capacitor, the charge passing through the top plate (metal), could not pass through to the other plate (bulk substrate) due to the presence of the silicon dioxide dielectric. Instead, a charge of +q is stored on the top plate and this will cause a charge of -q to be formed at the bottom plate [11]. The gate charge form at the metal gate is equal and opposite to the bulk charge in the silicon substrate [12]. Taking that P1 has the largest metal plate area, it relates to the highest value of capacitance because of its capability to store more charge on the plate. This will then be followed by an increase in the electric field and eventually the capacitance.

Experimental data also shows that the capacitance density obtained by the SOD doping method is more affected by the plate size because the differences in capacitance value is more obvious for P1, P2 and P3. This is because the contact between the oxide and aluminum metal is stronger due to the relatively high average roughness of the doped surface using SOD [13].

## VI. CONCLUSION

It is clear that various parameters such as doping methods, type of dopant species and plate sizes do affect the capacitance of a silicon based capacitor. It is shown that diffusion by SOD gives a higher capacitance density compared to diffusion by SS and that a larger plate size would contribute to a larger capacitance. The experiment also shows that n-type wafer heavily doped with phosphorus exhibits a higher capacitance density. Several properties that affect the thickness of the oxide layer grown such as the segregation and oxidation mechanism at specific temperatures will also affect the capacitance density.

For the future development of the silicon based capacitor, various considerations should be taken during the fabrication process. The characteristics of the silicon based capacitor could be improved by considering different "drive-in" and thermal oxidation duration. Dry oxidation can be considered as the oxidation method since it is known to give a better oxide quality. This is because the oxide dielectric plays a critical role in the characteristics of the silicon based capacitor. Furthermore, the type of oxide could also be varied to substitute the SiO<sub>2</sub> dielectric layer presently used. Hence, further study is also needed to determine segregation properties of impurities in these dielectric types.

## ACKNOWLEDGEMENT

We would like to thank all of the individuals who are directly and indirectly involved and for making it possible for us to successfully complete the research.

## REFERENCES

- [1] T. L. Floyd, Principles of Electric Circuits: Electron Flow Version, 8th Ed, Prentice Hall, 2007.

- [2] C. S. You, Semiconductor Manufacturing Technology: Advance Series in Electrical and Computer Engineering, vol13, World Scientific, 2008.

- [3] J. Bird, Electrical Circuit Theory and Technology, 3rd Ed, Newness Publication, 2007.

- [4] M.S. Tyagi, Minority Carrier Recombination in Heavily-doped Silicon, Solid-Slate Electronics Vol. 26, No. 6, pp. 577-597, 1983

- [5] P. V. Zant, Microchip Fabrication: A Practical Guide to Semiconductor Processing, Mc Graw Hill, 2000.

- [6] N. T. Nguyen, Spin-On Glass Materials and Applications in Advanced IC Technologies, Thesis, Universiteit Twente, Vietnam, 1970.

- [7] S. Wolf, Silicon Processing for the VLSI Era, Volume 1: Processing Technology, Lattice Press, 1986.

- [8] G. A. Haas and H. F. Gray, Oxidation of Oxide Surfaces, Journal of Applied Physics, Vol.46, No. 9, (1975).

- [9] B. Al-Kareh, Fundamentals of Semiconductor Processing Technologies, Kluwer Academic Publisher, 1995.

- [10] B. E. Deal and M. Sklar, Thermal Oxidation of Highly Doped Silicon, J. Electrochem. Soc., Volume 112, Issue 4, pp. 430-435 (1965).

- [11] R. A. DeCarlo and P.M. Lin, Linear Circuit Analysis, Oxford University Press, 2001.

- [12] Roger T. Howe and Charles G. Sodini, Microelectronics: An Integrated Approach, Prentice Hall, 1997.

- [13] C. Iliescua, M. Carpb, J. Miaoc, F. E. H. Taya and D. P. Poenarb, Analysis of Highly Doping with Boron from Spin-on Diffusing Source, Surface & Coatings Technology 198 (2005) 309–313.

Ahmad Sabirin Zoolfakar received his Bachelor in Electrical Engineering from Malaya University in 2001 and MSc in Microelectronic System and Telecommunication at The University of Liverpool, United Kingdom in 2002. He is a Member of IEEE Malaysia Section and member of BEM. He has been working with NEC (M) Sdn. Bhd and MIMOS Berhad.

Currently, he is working with UiTM Malaysia as a lecturer. His areas of research interest are semiconductor fabrication and devices.

Ahmad Akmalhakim Yaacob has been with the Faculty of Electrical Engineering at the Universiti Teknologi MARA (UiTM), Shah Alam since 2006. He is still enrolling in his final year to obtain a Bachelor of Electrical Engineering majoring in Electronics. His area of interest in research is mainly focused on the

semiconductor fabrication. He is a student member of the IEEE Malaysia Section and the Intel Elite student group in UiTM.

MaizatulZolkaplireceivedherBachelor inElectricalandElectronicEngineeringfromUniversitiTenagaNasional in2001andjustcompletedMScinMicroelectronicEngineeringatUniversitiMalaysiaPerlis.Shehasbeenactivelyinvolvedinsemiconductormanufacturingtechnologysince2001Priorto

joining the Faculty of Electrical Engineering, UiTM Shah Alam, she worked with LSI Logic in Gresham, OR, USA, Silterra Malaysia Sdn Bhd, MIMOS Berhad and Freescale Semiconductor Malaysia Sdn Bhd. She is a member of IEEE Malaysia Section. Her research interests are in the area of microfluidic, semiconductor fabrication and devices.

Azlan Zakaria received his Bachelor of Science in Chemistry in 1990 from University of Kentucky, USA and MSc in Microelectronic Materials and Devices Technology from UMIST, UK in 1995. Prior to joining Faculty of Applied Science, UiTM, Shah Alam, he had been working with MIMOS Berhad for 16 years in the

wafer fabrication plant. His current research interests are in the area of semiconductor material, devices and organic electronics.

Mohd Zahrin Abdul Wahab received his Bachelor in Physics from Universiti Kebangsaan Malaysia in 1995 and now he is doing Masters in Microelectronics at Universiti Kebangsaan Malaysia, Malaysia. He has 15 years of experience in Semiconductor Device, Simulation, Reliability and Parametric Testing.

Currently, he is working with MIMOS Wafer Fab as a Staff Engineer for Test, Reliability and Calibration Department.