# Statistical Optimization Influence on High Permittivity Gate Spacer in 16nm DG-FinFET Device

Ameer F. Roslan, F. Salehuddin\*, A.S.M. Zain, K.E. Kaharudin, N.R. Mohamad, Afifah Maheran A.H, H. Haroon, H.A. Razak, S.K. Idris Faculty of Electronic and Computer Engineering, Universiti Teknikal Malaysia Melaka (UTeM), 76100 Durian Tunggal, Melaka \*fauziyah@utem.edu.my

I.Ahmad

College of Engineering, Universiti Tenaga Nasional (UNITEN), Jalan Ikram-UNITEN, 43000 Kajang, Selangor

# ABSTRACT

In this paper, the effect of high permittivity gate spacer on short channel effects (SCEs) for the 16 nm double-gate finFET is investigated, with the output responses optimized using L9 orthogonal array (OA) Taguchi method. The determination is done through Signal-to-noise ratio to the effectiveness of the process parameters towards four output responses such as threshold voltage  $(V_{TH})$ , drive current  $(I_{ON})$ , leakage current  $(I_{OFF})$  and Subthreshold Swing (SS). The virtual fabrication of the 16 nm double-gate fin FET was performed using ANTHENA module while the electrical characteristics of the device were simulated using ATLAS module. These two modules were combined with Taguchi method to aid in designing and optimizing the process parameters. The electrical characterization was performed and significant improvement could be seen on the TiO<sub>2</sub> and HfO<sub>2</sub> material in terms of the  $I_{ON}/I_{OFF}$  ratio obtained at  $4.03 \times 10^6$  and  $3.61 \times 10^6$  respectively for  $0.179 \pm 12.7\%$  V of V<sub>TH</sub>. It can be observed that when approaching a higher value of dielectric constant (high-K), the  $I_{ON}$  increases while the SS and  $I_{OFF}$  decreases. As conclusion, the output responses from high-K materials have been proven to meet the minimum requirement by International Technology Roadmap Semiconductor (ITRS) 2013 for high performance Multi-Gate technology for the year 2015.

**Keywords:** *Double-gate FinFET; NMOS Device; Orthogonal Array; Taguchi Method; Statistical Method*

#### Introduction

Several of classification of electronic devices consumed today that includes mobile phone, computer, smart systems in home equipment for which become increasingly thin, lightweight, and compact in order to make electronics more flexible and portable. That said, smaller devices demand has forced the electronic industry to revolutionize the CMOS technology embedded in the devices altogether as well. On top of that, Moore's Law scaling prediction suppression can be done through the proposed new semiconductor devices and applications [1, 2]. Various types of Metal Oxide Semiconductor Field Effect Transistor (MOSFET) have been developed since then, while size of integrated devices reduces day by day with higher demand in multiple operations and therefore, causing size of MOSFETs which is the main component in memory and processors to be scaled down [3]–[9]. The reduction to nanometer regime has triggered the short channel effects to arise which degrades the system performance and reliability [10]. The devices performance may have been degraded via scaling process for the transistor miniaturization. The short channel effects (SCEs) have affected the device and the performance of the circuit in electron drift characteristics limitation within the channel, besides the reconstruction of the threshold voltage.

Therefore, a fin-shaped field effect transistor (FinFET) has been established in mitigating the SCEs in the occurrences of the more conventional planar MOSFET that have triggered the SCEs in the shrinking process. Constant challenges towards electrical definition to the parameter variations have also been studied [11]. Other than that, the performances of the transistor can be materialized through the implementation of FinFET. That said, the transconductance, carrier mobility and other possible parameters of the devices can be manipulated whereby the performance of the device can be hugely affected with the reduction to the channel length. Other introductions to the improvement of short channel performance includes the drain-induced barrier lowering (DIBL), subthreshold swing (SS) as well as threshold voltage ( $V_{TH}$ ) roll-off that could yield enhancement to that of the desired results. The FinFET design of 16nm technology is designed along with the performance of the transistor that is improved in relation to the Moore's Law alongside the considerations on reducing the depletion depth of the silicon and also the gate oxide thickness to the proportion of the gate length. Therefore, the gate oxide thickness and the gate-controlled junction or depletion depth in the silicon have to be reduced in proportion to L (Gate Length).

In complimenting the enhancement of design processes in the Polysilicon/Silicon Dioxide (PolySi/SiO<sub>2</sub>)-based DG-FinFET, several types of materials have been chosen with different constants, for which may significantly improve the output responses in threshold voltage level ( $V_{TH}$ ), drive current ( $I_{ON}$ ), leakage current ( $I_{OFF}$ ), and sub-threshold swing (SS), with

four parameters chosen. Appropriate statistical analysis techniques have been implemented to apply the input process parameter optimization from data collected, as proven by others through the implementation of statistical method to improve the robustness of nanoelectronics engineering [12]–[18]. The optimization has been succeeded in process parameters via the application of Taguchi method by Salehuddin et al. and Afifah et al. for which the authors have underlined the optimization of both  $V_{TH}$  and  $I_{OFF}$  for a 45 nm besides lowering the  $I_{OFF}$  whilst nominalized the  $V_{TH}$  for a 22 nm design in addition to the execution of high-k/metal gate for the design [19]–[23]. In this case, the process optimization is utilized towards three different spacer materials.

Other than that, in obtaining the desired threshold  $V_{TH}$ ,  $I_{ON}$ ,  $I_{OFF}$ , and SS, several device characteristics is studied and optimized by implementing  $L_9$  orthogonal array (OA) Taguchi statistical method since the variations of the process parameters may result in variations to the output responses [4]. The simulation based fabrication is done rather than the actual fabrication since it is proven to be more cost effective since it allows repetition to the experiment while the actual fabrication would have cost a lot more had the experiment to be done several times with variations in parameters. Besides, the disadvantage of the actual fabrication that is less feasible in gathering the immeasurable information however can take its place with virtual fabrication. The implementation of Taguchi method in this study is none other than the fact that the technique is extremely time effective as well as the robustness it is providing. Besides, Taguchi method also eases the actual fabrication process since its complexity increases as the device approaches the nanometer regime [18].

## **Methods and Materials**

#### **Device fabrication**

The construction of 16nm DG-FinFET as shown in Table 1 in this study has been succeeded with the utilization of the ATHENA and ATLAS modules from Silvaco International for the virtual process simulation as both tools serve differently in obtaining the respective physical characterisations and its electrical characterisations. Additionally, five geometrical parameters that is identified in its ability to trigger variations towards the output responses whereby the variations may also be caused by the fluctuations to the process parameter over the variations to the local parameters that are 30% from the overall [19].

The physical structure mesh simulation is developed for a P-type silicon with the employment of substrate orientation at <100> for which is followed by the formation of the oxide layer on the silicon bulk that is purposed as mask during the implantation of P-well. Subsequent to the gate terminal that is

secluded from both source and drain, for which opposes the conductive channel by a dielectric layer, Boron is infused into the silicon substrate for  $1 \times 10^{17}$  atom/cm<sup>3</sup> before the gate oxide is established for 870 °C with 3% of hydrochloric acid (HCl) in dry oxygen condition at 1 atmospheric pressure. Subsequently, the variation in threshold voltage can also be achieved with Boron implanted for  $1.95 \times 10^{13}$  atom/cm<sup>3</sup> with 5 KeV of energy in the channel region. Conclusively minor alterations on the gate concentration shall produce a significant difference to the variations of the said output responses. This phenomenon allows four most significant process parameters to be chosen based on the output responses produced with the same levels of parameter alterations. Subsequent to the deposition of polycrystalline silicon on the semiconductor wafer as the formation is succeeded to the multi-layered structure, the conformal polysilicon process follows.

$\begin{tabular}{|c|c|c|c|c|} \hline Parameters & Value (nm) \\ \hline Gate Length, L_G & 16 \\ SiO_2 Thickness, T_{OX} & 3.25 \\ Main substrate (silicon) length, L_C & 35 \\ Polysilicon Length, L_{DM} & 17.3 \\ Silicon Thickness, T_{FIN} & 18.7 \\ \hline \end{tabular}$

Table 1: Minimum values of spacing and edge and end distances

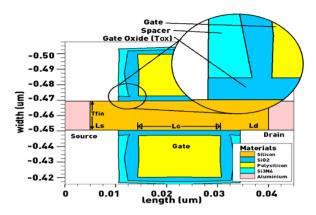

The utilisation of indium as a dopant for  $1.17 \times 10^{13}$  atom/cm<sup>3</sup> along with 1 KeV of energy has allowed the reduction in SCEs specifically for n-type doped Source/Drain (S/D) areas alongside the p-type substrate. The construction of sidewall spacer with the development of Si<sub>3</sub>N<sub>4</sub> layer to the surface of both silicon and polysilicon. Implant of arsenic dose is compensated at  $22 \times 10^{18}$  atom/cm<sup>3</sup> with 3 KeV of implant energy formation to the S/D implantation, for which allowing the reduction inside capacitance. Metallization process taken its place through aluminium deposition followed by the patterning based on the formation of contact window in the S/D region before the structure is mirrored and defined. The final structure of the device is fabricated via simulated as shown in Figure 1. The optimization process follows the virtual fabrication process through an orthogonal array with three different levels based on process parameters chosen and that is identified to have shown significant changes towards the output responses.

Figure 1: A simulated structure of the PolySi/SiO<sub>2</sub>-based DG-FinFET.

#### Optimization using L9 Orthogonal Array for Taguchi method

The L9 orthogonal array (OA) selection has been due to the fact that it is suitable in the optimization environment that requires four relevant process parameters added to three different levels alongside two noise factors. The implementation of L9 and its experimental layout is as shown in Table 2 and Table 3, for each represents four process parameters and its levels, and the noise factor respectively. These range of value are within the standard ranges of semiconductor doping utilized in real fabrication process [24, 25]. V<sub>TH</sub> doping dose, V<sub>TH</sub> doping tilt, polysilicon doping dose and polysilicon doping tilt are all included in the process parameters with three different levels; where each is symbolled as A, B, C and D respectively. However, the V<sub>TH</sub> doping dose differs depending on the material used since each material holds different permittivity values with Si<sub>3</sub>N<sub>4</sub> with k = 9.5, HfO<sub>2</sub> with k = 25 and TiO<sub>2</sub> with k = 85 that produces different output responses.

The inclusion for the noise factor is required in the statistical designed by the Taguchi approach. That said, both gate oxide temperature, Y and polysilicon oxidation temperature, Z as both may minorly bringing some changes to the results. This is due to that the local parameter variations affects the changes in output responses by a third of the overall variations, given that the local parameter is varied. Performance improvement of the integrated circuits meanwhile have spurred the parameter fluctuation control for which consequently affecting the scaling process. That said the circumstances in the scaling process is also affected from increment in parameter variation. Meanwhile, the selection of L9 OA has been largely due to the total degree of freedoms whereby the differences in the output responses can be studied via the determination of the three-levelled OA from the lowest to the most. Throughout 9 experiments for three different arrays, combination of four

#### Ameer F. Roslan et al.

simulation experiments were held since the four experiments consisted in a single combination factor, were projected from two levels that is unified to two noise factors in  $Y_1Z_1$ ,  $Y_1Z_2$ ,  $Y_2Z_1$ , and  $Y_2Z_2$ .

| Factor     | Process Parameter Control Factor |            |             |             |  |  |

|------------|----------------------------------|------------|-------------|-------------|--|--|

|            | А                                | В          | С           | D           |  |  |

| Experiment | VTH Doping                       | VTH Doping | Polysilicon | Polysilicon |  |  |

| No.        | Dose                             | Tilt       | Doping Dose | Doping Tilt |  |  |

| 1          | 1                                | 1          | 1           | 1           |  |  |

| 2          | 1                                | 2          | 2           | 2           |  |  |

| 3          | 1                                | 3          | 3           | 3           |  |  |

| 4          | 2                                | 1          | 2           | 3           |  |  |

| 5          | 2                                | 2          | 3           | 1           |  |  |

| 6          | 2                                | 3          | 1           | 2           |  |  |

| 7          | 3                                | 1          | 3           | 2           |  |  |

| 8          | 3                                | 2          | 1           | 3           |  |  |

| 9          | 3                                | 3          | 2           | 1           |  |  |

Table 2: Experimental layout using 19 orthogonal array

Table 3: Experimental layout using 19 orthogonal array

| Process Parameters         |                                 | Unit                 | Level 1                  | Level 2                | Level 3                  |

|----------------------------|---------------------------------|----------------------|--------------------------|------------------------|--------------------------|

| VTH                        | Si <sub>3</sub> Ni <sub>4</sub> | _                    | 3.85 x10 <sup>13</sup>   | 3.87 x10 <sup>13</sup> | 3.89 x10 <sup>13</sup>   |

| Doping                     | HfO <sub>2</sub>                | atom/cm <sup>3</sup> | 3.75 x10 <sup>13</sup>   | 3.77 x10 <sup>13</sup> | 3.79 x10 <sup>13</sup>   |

| Dose                       | TiO <sub>2</sub>                | _                    | 3.75 x10 <sup>13</sup>   | 3.77 x10 <sup>13</sup> | $3.79 \text{ x} 10^{13}$ |

| VTH Dopin                  | VTH Doping Tilt                 |                      | 5                        | 6                      | 7                        |

| Polysilicon Doping<br>Dose |                                 | atom/cm <sup>3</sup> | $2.10 \text{ x} 10^{14}$ | 2.12 x10 <sup>14</sup> | 2.14 x10 <sup>14</sup>   |

| Polysilicon<br>Tilt        | Doping                          | deg.                 | -22                      | -21                    | -20                      |

Table 4: Noise Factor of PolySi/SiO<sub>2</sub>-based FinFET

| Noise Factor                         | Units | Level 1 | Level 2 |

|--------------------------------------|-------|---------|---------|

| Gate oxidation temperature, Y        | °C    | 870     | 875     |

| Polysilicon oxidation temperature, Z | °C    | 870     | 875     |

Each output responses desires different optimization characteristics, with  $V_{TH}$  classed as nominal-the-best (NTB), for which the  $V_{TH}$  is aimed at 0.179 V or within 12.7% of the value selected. I<sub>ON</sub> meanwhile is targeted to be 1700  $\mu$ A/ $\mu$ m or preferably higher than that and therefore best apply to larger-the-best (LTB) in order to achieve as high as possible given that the other output responses are achieving the targeted values. With I<sub>OFF</sub> and SS requiring

values that are as minimum as possible, with  $I_{OFF}$  required to achieve lower than 100 pA/µm; the smaller-the-best (STB) characteristics is implemented to these aforementioned output responses. The values of SNR (ŋ) for the NTB, LTB and STB can be achieved with the dedicated equations in Equation (1), Equation (4) and Equation (5), respectively [26-28]:

$$\eta_{\rm NTB} = 10 \log_{10}[\mu^2/\sigma^2]$$

(1)

where,

$$\mu = (Y_i + \dots + Y_n)/n \tag{2}$$

and

$$\sigma^{2} = \sum_{i=1}^{n} (Y_{i} - \mu)^{2} / (n - 1)$$

<sup>(3)</sup>

$$\eta_{\text{STB}} = 10 \log_{10} \left[ \frac{1}{n} \sum (Y_1^2 + Y_2^2 + \dots + Y_n^2) \right]$$

(4)

$$\eta_{\rm LTB} = 10 \log_{10} \left[ \frac{1}{n} \sum \left( (1/Y_1^2) + (1/Y_2^2) + \dots + (1/Y_n^2) \right) \right]$$

(5)

The experimental values for the output responses characteristics, as well as the number of tests and the value of the experimental responses are all represented by the respective  $\eta$  and  $Y_n$ . Consequently, the characteristics of experimental design's orthogonal allows every effect on the process parameter of the SNR to be break out at different levels. Through the implementation of the equation (1)-(5), the acquisition of mean, variance and SNR values for the PolySi/SiO<sub>2</sub> FinFET for spacer materials of Si<sub>3</sub>N<sub>4</sub>, HfO<sub>2</sub>, and TiO<sub>2</sub> are gathered as in Tables 5, 6 and 7, respectively.

|             | V <sub>TH</sub> |          |                       |                      |                      | IOFF                 | SS               |

|-------------|-----------------|----------|-----------------------|----------------------|----------------------|----------------------|------------------|

| Exp.<br>No. | Mean            | Variance | SNR<br>(Mean)<br>(dB) | SNR<br>(NTB)<br>(dB) | SNR<br>(LTB)<br>(dB) | SNR<br>(STB)<br>(dB) | SNR(STB)<br>(dB) |

| 1           | 0.176           | 9.81E-06 | -15.10                | 34.98                | 64.75                | -57.52               | -39.51           |

| 2           | 0.178           | 8.69E-06 | -15.00                | 35.60                | 65.71                | -60.40               | -39.56           |

| 3           | 0.177           | 8.72E-06 | -15.02                | 35.57                | 66.05                | -62.47               | -39.61           |

| 4           | 0.182           | 8.96E-06 | -14.78                | 35.70                | 66.01                | -61.36               | -39.61           |

| 5           | 0.180           | 1.06E-05 | -14.89                | 34.85                | 64.77                | -56.69               | -39.51           |

| 6           | 0.182           | 8.71E-06 | -14.80                | 35.80                | 65.67                | -59.47               | -39.56           |

| 7           | 0.187           | 8.80E-06 | -14.56                | 36.00                | 65.64                | -58.45               | -39.55           |

| 8           | 0.187           | 9.33E-06 | -14.58                | 35.72                | 65.97                | -60.43               | -39.60           |

Table 5: Mean, variance and S/N Ratio for  $V_{TH},\,I_{ON},\,I_{OFF}$  and SS for  $Si_3N_4$  spacer on PolySi/SiO\_2-based FinFET

Table 6: Mean, variance and S/N Ratio for  $V_{TH},\,I_{ON},\,I_{OFF}$  and SS for  $HfO_2$  spacer on PolySi/SiO\_2-based FinFET

|             |       | V        | V <sub>TH</sub>       |                      | I <sub>ON</sub>      | I <sub>OFF</sub>     | SS               |

|-------------|-------|----------|-----------------------|----------------------|----------------------|----------------------|------------------|

| Exp.<br>No. | Mean  | Variance | SNR<br>(Mean)<br>(dB) | SNR<br>(NTB)<br>(dB) | SNR<br>(LTB)<br>(dB) | SNR<br>(STB)<br>(dB) | SNR(STB)<br>(dB) |

| 1           | 0.179 | 6.75E-06 | -14.96                | 36.75                | 64.20                | -51.64               | -39.43           |

| 2           | 0.177 | 5.22E-06 | -15.05                | 37.77                | 65.34                | -55.16               | -39.44           |

| 3           | 0.174 | 4.63E-06 | -15.18                | 38.17                | 65.72                | -57.40               | -39.45           |

| 4           | 0.179 | 4.69E-06 | -14.92                | 38.36                | 65.67                | -60.92               | -39.45           |

| 5           | 0.183 | 6.71E-06 | -14.75                | 36.98                | 64.23                | -51.70               | -39.43           |

| 6           | 0.181 | 5.17E-06 | -14.84                | 38.03                | 65.29                | -54.21               | -39.44           |

| 7           | 0.186 | 5.07E-06 | -14.59                | 38.36                | 65.27                | -53.19               | -39.45           |

| 8           | 0.184 | 4.70E-06 | -14.71                | 38.56                | 65.63                | -55.33               | -39.45           |

|             |       | ١        | / <sub>TH</sub>       |                      | Ion                  | IOFF                 | SS               |

|-------------|-------|----------|-----------------------|----------------------|----------------------|----------------------|------------------|

| Exp.<br>No. | Mean  | Variance | SNR<br>(Mean)<br>(dB) | SNR<br>(NTB)<br>(dB) | SNR<br>(LTB)<br>(dB) | SNR<br>(STB)<br>(dB) | SNR(STB)<br>(dB) |

| 1           | 0.178 | 9.74E-06 | -15.01                | 35.10                | 64.36                | -51.91               | -39.39           |

| 2           | 0.177 | 6.03E-06 | -15.03                | 37.17                | 65.55                | -55.40               | -39.40           |

| 3           | 0.175 | 4.77E-06 | -15.12                | 38.10                | 65.93                | -57.62               | -39.41           |

| 4           | 0.181 | 5.22E-06 | -14.87                | 37.96                | 65.89                | -56.50               | -39.41           |

| 5           | 0.182 | 9.74E-06 | -14.80                | 35.31                | 64.39                | -51.12               | -39.39           |

| 6           | 0.182 | 6.17E-06 | -14.82                | 37.28                | 65.51                | -54.45               | -39.40           |

| 7           | 0.187 | 6.20E-06 | -14.57                | 37.50                | 65.49                | -53.44               | -39.40           |

| 8           | 0.185 | 5.41E-06 | -14.65                | 38.01                | 65.85                | -55.56               | -39.42           |

Table 7: Mean, variance and S/N Ratio for  $V_{TH}$ ,  $I_{ON}$ ,  $I_{OFF}$  and SS for TiO<sub>2</sub> spacer on PolySi/SiO<sub>2</sub>-based FinFET

## **Results and Analysis**

### ANOVA for optimization

The analysis of variance (ANOVA) is capitalized by divisions of variance for which allows the output response variations can be achieved based on the process parameter set. The relative power factor is denoted by the factor effect percentage of SNR, which is affecting the reduction towards variation whereby the larger percentage contribution indicates larger significance towards the performance. Based on Table 8, for which is the factor effect towards the responses of V<sub>TH</sub>, I<sub>ON</sub>, I<sub>OFF</sub> and SS for the device with Si<sub>3</sub>N<sub>4</sub> spacer, polysilicon doping tilt for factor D showcases significance with 100% and 99% contribution for I<sub>ON</sub> and SS and is dominant towards V<sub>TH</sub> and I<sub>ON</sub> with 71% and 86% respectively. V<sub>TH</sub> doping dose contributes 19% as well towards V<sub>TH</sub> which is highest among other output responses. However, both V<sub>TH</sub> doping tilt and polysilicon shows highest percentage contribution at only 8% and 2% towards V<sub>TH</sub>, for which is insignificant towards variations of the responses. That said, output responses I<sub>ON</sub>, I<sub>OFF</sub> and SS will highly reactive towards variations on the tilt to the polysilicon doping.

The reaction for the output responses for the device with  $HfO_2$  spacer in Table 9 showcases similar reactions towards the parameter variations.  $V_{TH}$ ,  $I_{ON}$ , and SS shows higher percentage factor against polysilicon doping tilt with significant 87%, 78% and 99% respectively, with only 35% dominant towards  $I_{ON}$ . However, the  $V_{TH}$  doping tilt,  $V_{TH}$  doping tilt and polysilicon doping dose for factor A, B and C showcases 22% contribution factor towards  $I_{\rm ON}$  with 12% and 14% percentage factor recorded towards  $V_{\rm TH}$  and  $I_{\rm OFF}$  for factor A.

| ,        | Symbol               | А                              | В                              | С                             | D                          |

|----------|----------------------|--------------------------------|--------------------------------|-------------------------------|----------------------------|

|          | Process<br>arameters | V <sub>TH</sub> Doping<br>Dose | V <sub>TH</sub> Doping<br>Tilt | Polysilicon<br>Doping<br>Dose | Polysilicon<br>Doping Tilt |

|          | Symbol               | A3                             | B3                             | C1                            | D2                         |

| 17       | % Factor             | 19                             | 8                              | 2                             | 71                         |

| $V_{TH}$ | Value                | 3.89 x10 <sup>13</sup>         | 7                              | $2.10 \text{ x} 10^{13}$      | -20                        |

|          | Symbol               | A2                             | B2                             | C2                            | D2                         |

| Ion      | % Factor             | 0                              | 0                              | 0                             | 100                        |

|          | Value                | $3.87 \text{ x} 10^{13}$       | 6                              | 2.12 x10 <sup>13</sup>        | -20                        |

|          | Symbol               | A3                             | B2                             | C2                            | D1                         |

| IOFF     | % Factor             | 14                             | 0                              | 0                             | 86                         |

|          | Value                | 3.89 x10 <sup>13</sup>         | 6                              | 2.12 x10 <sup>13</sup>        | -22                        |

|          | Symbol               | A2                             | B2                             | C2                            | D1                         |

| SS       | % Factor             | 1                              | 0                              | 0                             | 99                         |

| 55       | Value                | 3.87 x10 <sup>13</sup>         | 6                              | 2.12 x10 <sup>13</sup>        | -22                        |

Table 8: Factor effect of S/N ratio for  $V_{TH},\,I_{ON},\,I_{OFF}$  and SS for  $Si_3N_4$  spacer on PolySi/SiO2-based DG-FinFET

Table 9: Factor effect of S/N ratio for  $V_{TH},\,I_{ON},\,I_{OFF}$  and SS for  $HfO_2$  spacer on PolySi/SiO\_2-based DG-FinFET

| Symb                  | ol       | А                              | В                              | С                             | D                          |

|-----------------------|----------|--------------------------------|--------------------------------|-------------------------------|----------------------------|

| Process<br>Parameters |          | V <sub>TH</sub> Doping<br>Dose | V <sub>TH</sub> Doping<br>Tilt | Polysilicon<br>Doping<br>Dose | Polysilicon<br>Doping Tilt |

|                       | Symbol   | A1                             | B2                             | C2                            | D3                         |

| V                     | % Factor | 12                             | 0                              | 0                             | 87                         |

| $V_{TH}$              | Value    | 3.75 x10 <sup>13</sup>         | 6                              | $2.12 \text{ x} 10^{13}$      | -20                        |

|                       | Symbol   | A1                             | B1                             | C3                            | D3                         |

| Ion                   | % Factor | 22                             | 22                             | 22                            | 35                         |

|                       | Value    | 3.75 x10 <sup>13</sup>         | 5                              | 2.14 x10 <sup>13</sup>        | -20                        |

|                       | Symbol   | A3                             | B2                             | C2                            | D1                         |

| IOFF                  | % Factor | 14                             | 4                              | 5                             | 78                         |

|                       | Value    | 3.79 x10 <sup>13</sup>         | 6                              | 2.12 x10 <sup>13</sup>        | -22                        |

|                       | Symbol   | A2                             | B2                             | C2                            | D1                         |

| SS                    | % Factor | 1                              | 0                              | 0                             | 99                         |

| 55                    | Value    | 3.77 x10 <sup>13</sup>         | 6                              | 2.12 x10 <sup>13</sup>        | -22                        |

Although Table 10 shows similar trends towards factor D for all process parameters at 96%, 100%, 89% and 87%, factor B and C show very minimum contribution to the responses with only SS might be varied with only 4% and 3% respectively. Factor A meanwhile shows minimum contribution towards  $V_{TH}$ , I<sub>OFF</sub> and SS with respective 2%, 11% and 6% and zero contribution towards variations of I<sub>OFF</sub>.

| Symb                  | ol       | А                              | В                              | С                             | D                          |

|-----------------------|----------|--------------------------------|--------------------------------|-------------------------------|----------------------------|

| Process<br>Parameters |          | V <sub>TH</sub> Doping<br>Dose | V <sub>TH</sub> Doping<br>Tilt | Polysilicon<br>Doping<br>Dose | Polysilicon<br>Doping Tilt |

|                       | Symbol   | A2                             | B2                             | C2                            | D3                         |

| <b>T</b> 7            | % Factor | 2                              | 1                              | 1                             | 96                         |

| $V_{TH}$              | Value    | $3.77 \text{ x} 10^{13}$       | 6                              | $2.12 \text{ x} 10^{13}$      | -20                        |

|                       | Symbol   | A2                             | B2                             | C2                            | D2                         |

| Ion                   | % Factor | 0                              | 0                              | 0                             | 100                        |

|                       | Value    | $3.77 \text{ x} 10^{13}$       | 6                              | $2.12 \text{ x} 10^{13}$      | -20                        |

|                       | Symbol   | A3                             | B2                             | C2                            | D1                         |

| IOFF                  | % Factor | 11                             | 0                              | 0                             | 89                         |

|                       | Value    | 3.79 x10 <sup>13</sup>         | 6                              | $2.12 \text{ x} 10^{13}$      | -22                        |

|                       | Symbol   | A1                             | B2                             | C2                            | D1                         |

| 66                    | % Factor | 6                              | 4                              | 3                             | 87                         |

| SS                    | Value    | 3.75 x10 <sup>13</sup>         | 6                              | 2.12 x10 <sup>13</sup>        | -22                        |

Table 10: Factor effect of S/N ratio for V<sub>TH</sub>, I<sub>ON</sub>, I<sub>OFF</sub> and SS for TiO<sub>2</sub> spacer on PolySi/SiO<sub>2</sub>-based DG-FinFET

#### Confirmation tests for output responses

Every response in  $V_{TH}$ ,  $I_{ON}$ ,  $I_{OFF}$  and SS has generated the output response desired that are optimized, with each classed by NTB, LTB and STB. That add comparisons have been made to each of the optimum response combination before best combination settings are made through selections of overall optimized response. The best combination settings are chosen by prioritization towards threshold voltage for which is nominal. Secondly, leakage current ( $I_{OFF}$ ) is prioritized ahead of  $I_{ON}$  and SS as higher  $I_{OFF}$  will likely suffer the values of  $I_{ON}/I_{OFF}$  ratio despite high  $I_{ON}$  achieved. The prioritization to the combinations has been chosen based on the hierarchical order from  $V_{TH}$ ,  $I_{OFF}$ ,  $I_{ON}$  and SS desired respectively. Subsequently, confirmation tests are run via best setting combination as in Tables 11, 12 and 13, each representing the FinFET device with  $S_3N_4$ , HfO<sub>2</sub> and TiO<sub>2</sub> in that order, for spacer materials.

| Symbol | Process Parameters         | Best Combination |          |                                              |  |

|--------|----------------------------|------------------|----------|----------------------------------------------|--|

|        | FIOCESS Farameters         | Symbol           | % Factor | Value                                        |  |

| А      | VTH Doping Dose            | A3               | 19       | 3.89 x10 <sup>13</sup> atom cm <sup>-3</sup> |  |

| В      | VTH Doping Tilt            | B3               | 8        | $7^{\circ}$                                  |  |

| С      | Polysilicon Doping<br>Dose | C1               | 2        | 2.10 x10 <sup>13</sup> atom cm <sup>-3</sup> |  |

| D      | Polysilicon Doping<br>Tilt | D2               | 100      | -21°                                         |  |

Table 11: Best setting combination for Si\_3N\_4 spacer on PolySi/SiO\_2-based DG-FinFET

Table 12: Best setting combination for  $HfO_2$  spacer on PolySi/SiO\_2-based DG-FinFET

| Symbol | Ducasas Donomators         | Best Combination |          |                                              |  |

|--------|----------------------------|------------------|----------|----------------------------------------------|--|

|        | Process Parameters         | Symbol           | % Factor | Value                                        |  |

| А      | VTH Doping Dose            | A1               | 22       | 3.75 x10 <sup>13</sup> atom cm <sup>-3</sup> |  |

| В      | VTH Doping Tilt            | B1               | 22       | 5°                                           |  |

| С      | Polysilicon Doping<br>Dose | C3               | 22       | 2.14 x10 <sup>13</sup> atom cm <sup>-3</sup> |  |

| D      | Polysilicon Doping<br>Tilt | D1               | 99       | -22°                                         |  |

Table 13: Best setting combination for  $TiO_2$  spacer on PolySi/SiO\_2-based DG-FinFET

| Symbol | Duo ooss Douomotous        | Best Combination |          |                                              |  |

|--------|----------------------------|------------------|----------|----------------------------------------------|--|

| Symbol | Process Parameters         | Symbol           | % Factor | Value                                        |  |

| А      | VTH Doping Dose            | A3               | 11       | 3.79 x10 <sup>13</sup> atom cm <sup>-3</sup> |  |

| В      | VTH Doping Tilt            | B3               | 0        | $7^{\circ}$                                  |  |

| С      | Polysilicon Doping<br>Dose | C2               | 3        | 2.12 x10 <sup>13</sup> atom cm <sup>-3</sup> |  |

| D      | Polysilicon Doping<br>Tilt | D1               | 89       | -22°                                         |  |

The results in Table 14 consists of initial simulated experiment, for which represents the responses achieved before it is optimized via Taguchi approach. Meanwhile, optimized simulations are achieved via simulation run based on the best setting combinations achieved from the aforementioned Tables 11, 12 and 13, with noise factor Y and Z in considerations whereby the noise factor along with the combination requires four runs for each spacer material design. The estimated value from the optimized simulations are also obtained through the SNR ranges achieved for each of the four parameters.

| Device<br>Characteristics                            | Pre-<br>optimized<br>Simulation | imized (Taguchi)<br>nulation Estimated Observed |                      | ITRS 2013<br>prediction<br>(target o/p)<br>[29] |

|------------------------------------------------------|---------------------------------|-------------------------------------------------|----------------------|-------------------------------------------------|

| Level                                                | $A_1B_1C_1D_1$                  |                                                 |                      |                                                 |

| $V_{TH}(V)$                                          | 0.1871                          | 0.167                                           | 0.1801               | 0.179                                           |

| % Diff from target                                   | 4.33                            | 6.70                                            | 0.61                 | -                                               |

| o/p<br>SNR-NTB (dB)                                  | 36.00                           | 35.5                                            | 34.85                | -                                               |

| I <sub>ON</sub> (μΑ/μm)<br>% Diff from target<br>o/p | 1916.87<br>11.31                | 1880.0<br>9.57                                  | 1740.97<br>2.35      | >1700                                           |

| SNR-LTB (dB)                                         | 65.64                           | 65.5                                            | 64.77                | -                                               |

| I <sub>OFF</sub> (nA/µm)                             | 0.812                           | 0.908                                           | 0.649                | <100                                            |

| % Diff from target                                   | 99.19                           | 99.09                                           | 99.35                | _                                               |

| o/p<br>SNR-STB (dB)                                  | -58.45                          | -59.20                                          | -56.69               | -                                               |

| Ion /Ioff ratio                                      | $2.36 \times 10^{6}$            | $2.07 \times 10^{6}$                            | $2.68 \times 10^{6}$ | $1.7 \times 10^{4}$                             |

| SNR-LTB (dB)                                         | -                               | -                                               | -                    | -                                               |

| SS (mV/dec)                                          | 93.18                           | 95.00                                           | 94.47                | N/A                                             |

| % Diff from target<br>o/p                            | -                               | -                                               | -                    | N/A                                             |

| SNR-STB (dB)                                         | -39.65                          | -39.6                                           | -39.51               | N/A                                             |

| Table 14: Comparisons between optimized value with combination of |  |  |  |  |  |  |

|-------------------------------------------------------------------|--|--|--|--|--|--|

| $A_3B_3C_1D_2$ and the ITRS prediction for $Si_3N_4$ spacer       |  |  |  |  |  |  |

Based on the results obtained, comprising the pre-optimized simulations, optimized solutions with the implementation of Taguchi statistical method, Tables 14, 15 and 16, V<sub>TH</sub> is shown to have achieved within  $\pm 12.7\%$  range from the targeted 0.179 V based on the roadmap provided by the ITRS 2013 based on the optimized results observed for Si<sub>3</sub>N<sub>4</sub>, HfO<sub>2</sub> and TiO<sub>2</sub>. This is to precisely evaluate the performance in terms of the corresponding I<sub>ON</sub>, I<sub>OFF</sub>, I<sub>ON</sub>/I<sub>OFF</sub> ratio, and SS of the aforementioned device. An improvement is showcased towards the ION/IOFF ratio on each of the optimized simulated experiments. This is due to the prioritization made towards lowering the  $I_{OFF}$  for which have significantly encouraged the rise in the I<sub>ON</sub>/I<sub>OFF</sub> ratio despite reduction in I<sub>ON</sub> after the optimization succeeded. The significance of having a very high value of the I<sub>ON</sub>/I<sub>OFF</sub> ratio because it is suitable for high-speed logic and low power application [30,31]. The  $I_{ON}/I_{OFF}$ ratio is at 2.68×10<sup>6</sup> after it is optimized compared to 2.36×10<sup>6</sup> for Si<sub>3</sub>N<sub>4</sub> spacer design, with another improvement on I<sub>ON</sub>/I<sub>OFF</sub> ratio for HfO<sub>2</sub> spacer design as well with  $3.61 \times 10^6$  from the previous  $3.29 \times 10^6$ . TiO<sub>2</sub> spacer design meanwhile showcased a major leap to  $4.03 \times 10^6$  from  $3.2829 \times 10^6$ . Besides, the V<sub>TH</sub>

#### Ameer F. Roslan et al.

approaches closer to 0.179 V for both Si<sub>3</sub>N<sub>4</sub> and HfO<sub>2</sub> with 0.61% and 1.16% respectively. Despite the slight increment towards the difference to 0.19% rather than 0.18% before optimized, the  $V_{TH}$  for TiO<sub>2</sub> spacer proves to achieved within ±12.7% range of 0.179 V [29].

| Device Characteristics                              | Pre-<br>optimized<br>Simulation<br>A <sub>1</sub> B <sub>1</sub> C <sub>1</sub> D <sub>1</sub> | (Tag<br>Estimated        | Simulation<br>guchi)<br>Observed<br>3C1D2 | ITRS 2013<br>prediction<br>(target value)<br>[29] |

|-----------------------------------------------------|------------------------------------------------------------------------------------------------|--------------------------|-------------------------------------------|---------------------------------------------------|

| V <sub>TH</sub> (V)                                 | 0.184                                                                                          | 0.129                    | 0.181                                     | 0.179                                             |

| % Diff from target o/p                              | 2.61                                                                                           | 27.93                    | 1.16                                      |                                                   |

| SNR (dB)                                            | 38.56                                                                                          | 37.81                    | 38.03                                     |                                                   |

| IoN (µA/µm)                                         | 1913.08                                                                                        | 1490.0                   | 1840.60                                   | >1700                                             |

| % Diff from target o/p                              | 12.53                                                                                          | 12.35                    | 8.27                                      |                                                   |

| SNR (dB)                                            | 65.63                                                                                          | 63.50                    | 65.29                                     |                                                   |

| IoFF (nA/μm)<br>% Diff from target o/p<br>SNR (dB)  | 0.582<br>99.42<br>-55.33                                                                       | 0.523<br>99.48<br>-54.40 | 0.510<br>99.49<br>-54.21                  | <100<br>-                                         |

| I <sub>ON</sub> /I <sub>OFF</sub> ratio<br>SNR (dB) | 3.29×10 <sup>6</sup>                                                                           | 2.85×10 <sup>6</sup>     | 3.61×10 <sup>6</sup>                      | 1.7×10 <sup>4</sup>                               |

| SS (mV/dec)                                         | 93.89                                                                                          | 93.80                    | 93.78                                     | N/A                                               |

| % Diff from target o/p                              | -                                                                                              | -                        | -                                         | N/A                                               |

| SNR (dB)                                            | -39.45                                                                                         | -39.44                   | -39.44                                    | N/A                                               |

Table 15: Comparisons between optimized value with combination of  $A_1B_1C_3D_1$  and the ITRS prediction for HfO<sub>2</sub> spacer

|                               | Pre-                 | Optimized Simulation<br>(Taguchi) |                      | ITRS 2013           |

|-------------------------------|----------------------|-----------------------------------|----------------------|---------------------|

| <b>Device Characteristics</b> | optimized            |                                   |                      | prediction          |

|                               | Simulation           | Estimated                         | Observed             | (target value)      |

| Level                         | $A_1B_1C_1D_1$       | $A_3B_3C_1D_2$                    |                      | [29]                |

| $V_{TH}(V)$                   | 0.185                | 0.143                             | 0.187                | 0.179               |

| % Diff from target o/p        | 0.61                 | 3.60                              | 0.78                 | -                   |

| SNR (dB)                      | 38.01                | 36.90                             | 35.88                | -                   |

| I <sub>ON</sub> (μΑ/μm)       | 1961.19              | 1830.00                           | 1882.35              | >1700               |

| % Diff from target o/p        | 15.36                | 7.65                              | 10.73                | -                   |

| SNR (dB)                      | 65.85                | 65.30                             | 64.33                | -                   |

| I <sub>OFF</sub> (nA/µm)      | 0.510                | 0.502                             | 0.597                | <100                |

| % Diff from target o/p        | 99.49                | 99.50                             | 99.40                | -                   |

| SNR (dB)                      | -55.56               | -54.1                             | -50.10               | -                   |

| Ion /Ioff ratio               | 3.28×10 <sup>6</sup> | 3.64×10 <sup>6</sup>              | 4.03×10 <sup>6</sup> | $1.7 \times 10^{4}$ |

| SNR (dB)                      | -                    | -                                 | -                    | -                   |

| SS (mV/dec)                   | 93.59                | 93.30                             | 93.34                | N/A                 |

| % Diff from target o/p        | -                    | -                                 | -                    | N/A                 |

| SNR (dB)                      | -39.42               | -39.40                            | -39.39               | N/A                 |

Table 16: Comparisons between optimized value with combination of  $A_3B_3C_2D_1$  and the ITRS prediction for TiO<sub>2</sub> spacer

# Conclusion

In conclusion, the DG-FinFET from simulations has established good electrical properties such as high drive current and low leakage current based on the electrical characteristic analyzed. With sufficing  $V_{TH}$  that is within the predicted  $\pm 12.7\%$  of 0.179 V, the TiO<sub>2</sub> and HfO<sub>2</sub> meanwhile have resulted in improvement of the device due to increment towards the  $I_{ON}/I_{OFF}$  ratio at respective  $4.03 \times 10^6$  and  $3.61 \times 10^6$  due to the permittivity of the material alongside the optimization that allows the values of  $I_{OFF}$  to be minimized despite lower  $I_{ON}$  acquired. It can be concluding that polysilicon doping tilt (factor D) is the most significant factor towards the output responses. That said, TiO<sub>2</sub>-materialed spacer with combination of  $A_3B_3C_2D_1$  shows the best  $I_{ON}/I_{OFF}$  ratio in conjunction to the device's power consumption efficiency. Besides that, the device characteristics have met the requirement of high performance (HP) multi-gate (MG) technology predicted by ITRS 2013 for the year 2015 requirements.

#### Acknowledgement

The authors would like to thank Micro and Nano Electronic (MiNE), Centre for Telecommunication Research and Innovation (CeTRI), Faculty of Electronics and Computer Engineering (FKEKK), Universiti Teknikal Malaysia Melaka (UTeM) for laboratory facilities and financial assistance throughout the project.

# References

- [1] H. Ilatikhameneh, T. Ameen, B. Novakovic, Y. Tan, G. Klimeck and R. Rahman, "Saving Moore's Law Down To 1 nm Channels With Anisotropic Effective Mass," *Scientific Reports*, pp. 31501, 2016.

- [2] S.M. Jagtap and V.J. Gond, "Study the performance parameters of novel scale FINFET Device in nm Region," *Proceedings of Electronics*, *Communication and Aerospace Technology (ICECA)*, vol. 1, pp. 424-430, 2017.

- [3] P. Sashmita, "Performance analysis of Single Gate and Double gate MOSFET with and without effect of noise," *Department of Electrical Engineering, National Institute of Technology*, Rourkela India, 2015.

- [4] Ahmed M. Dinar, A.S.M. Zain, and F. Salehuddin, "Comprehensive identification of sensitive and stable ISFET sensing layer high-k gate based on ISFET/electrolyte models," *International Journal of Electrical and Computer Engineering*, vol. 9, no. 2, pp. 926-933, 2018.

- [5] J. Song, J. Dailey, H. Li, H.J. Jang, P. Zhang, J.T.H. Wang and H.E. Katz, "Extended Solution Gate OFET-Based Biosensor for Label-Free Glial Fibrillary Acidic Protein Detection with Polyethylene Glycol-Containing Bioreceptor Layer," *Advanced Functional Materials*, vol. 2017, no. 27, pp. 1606506(1)- 1606506(7), 2017.

- [6] A. Uhlemann, K. Weidner, G. Mitic and S. Stegmeier, "Reliability study of SiC-JFET including new copper, planar and silver based interconnection and joining technologies," CISP 2016; 9<sup>th</sup> International Conference on Integrated Power Electronics Systems, pp. 1-7, 2016.

- [7] K.S. Li, P.G Chen, T.Y. Lai, C.H. Lin, C.C. Cheng, C.C. Chen and C. Hu, "Sub-60mV-swing negative-capacitance FinFET without hysteresis," *IEEE International Electron Devices Meeting (IEDM)*, pp. 2261-2264, 2015.

- [8] J. Ma and E. Matioli, "High Performance Tri-Gate GaN Power MOSHEMTs on Silicon Substrate," *IEEE Electron Device Letters*, vol. 38, no. 3, pp. 367–370, 2017.

- [9] L. Chen, F. Cai, U. Otuonye and W.D Lu, "Vertical Ge/Si Core/Shell Nanowire Junctionless Transistor," *Nano Letters*, vol. 16, no. 1, pp. 420–

Statistical Optimization Influence on High-K Material Gate Spacer in DG-FinFET Device

426, 2015.

- [10] D. Bhattacharya and N.K. Jha, "Review Article FinFETs : From Devices to Architectures," *Advances in Electronics, Hindawi Publishing Corporation*, vol. 2014, pp. 1-21, 2014.

- [11]S. Karapetyan, V. Kleeberger and U. Schlichtmann, "FinFET-based product performance: Modeling and evaluation of standard cells in FinFET technologies," *Microelectronics Reliability*, vol. 61, no. c, pp. 30– 34, 2016.

- [12] S. Mei, N. Raghavan, M. Bosman, D. Linten, G. Groeseneken, N. Horiguchi and K.L. Pey, "New understanding of dielectric breakdown in advanced FinFET devices — physical, electrical, statistical and multiphysics study" *IEEE International Electron Devices Meeting* (*IEDM*), pp. 15.5.1-15.5.4, 2016.

- [13] Y. Yu and N.K. Jha, "Statistical Optimization of FinFET Processor Architectures under PVT Variations Using Dual Device-Type Assignment," ACM Journal on Emerging Technologies in Computing Systems, vol. 14, no. 1, pp. 1–25, 2017.

- [14] N. Atan, B.Y. Majlis, I. Ahmad, K.H. Chong, "Analysis the Effect of Control Factors Optimization on the Threshold Voltage of 18 nm PMOS Using L27 Taguchi Method," *Indonesian Journal of Electrical Engineering and Computer Science*, vol. 10, no. 3, pp. 934-942, 2018.

- [15] S. Fu, Y. Mei, X. Li, C. Ma and G.Q. Lu, "A Multichip Phase-Leg IGBT Module Bonded by Pressureless Sintering of Nanosilver Paste," *IEEE Transactions on Device and Materials Reliability*, vol. 17, no. 1, pp. 146–156, 2017.

- [16] S. Chaudhuri, A.N. Bhoj, D. Bhattacharya, & N.K. Jha, "Fast FinFET Device Simulation under Process-Voltage Variations Using an Assisted Speed-Up Mechanism," *Proceedings on VLSI Design and Embedded Systems (VLSID)*, pp. 300-305, 2016.

- [17] S. Ichino, A. Teramoto, R. Kuroda, T. Mawaki, T. Suwa and S. Sugawa S, "Statistical Analysis of Threshold Voltage Variation Using MOSFETs with Asymmetric Source and Drain," *IEEE Electron Device Letters*, vol. 39, no. 12, pp. 1-4, 2018.

- [18] H. Elgomati, B.Y. Majlis, I. Ahmad, F. Salehuddin, F.A. Hamid, A. Zaharim, T.Z. Mohamad and P.R Apte PR, "Statistical Optimization for process parameters to reduce variability of 32 nm PMOS transistor Threshold voltage," *International Journal of the Physical Sciences*, vol. 6, no. 10, pp. 2372-2379, 2011.

- [19] K.E. Kaharudin, A.H. Hamidon and F. Salehuddin, Design and Optimization Aprroaches in Double Gate Device Architecture. *International Journal of Engineering and Technology (IJET)* 6(5), pp. 2070-2079, 2014.

- [20] A.H. Afifah Maheran, P.S. Menon, I. Ahmad, Z.A. Noor Faiza, A.S.M.

Zain, F. Salehuddin and N.M. Sayed, "Threshold voltage and leakage current variability on process parameter in a 22nm PMOS Device," *Journal of Telecommunication, Electronic and Computer Engineering*, vol. 10, no. 2-8, pp. 9-13, 2018.

- [21] K.E. Kaharudin, F. Salehuddin, A.S.M. Zain and M.N.I.A. Aziz, "Taguchi Modelling with the Interaction Test for Higher Drive Current in WSIx/TIO2 Channel Vertical Double Gate NMOS Device," *Journal of Theoretical and Applied Information Technology*, vol. 90, no. 1, pp. 185– 193, 2016.

- [22] F. Salehuddin, A.S.M. Zain, N.M. Idris, A.K.M. Yamin, A.M.A. Hamid, I. Ahmad and P.S. Menon, "Analysis of Threshold Voltage Variance in 45nm N-Channel Device Using L27 Orthogonal Array Method," *Advanced Material Research*, vol. 903, pp. 297–302, 2014.

- [23] K.E. Kaharudin, A.H. Hamidon and F. Salehuddin, "Design and Optimization Approaches in Double Gate Device Architecture," *International Journal of Engineering and Technology (IJET)*, vol. 6, no. 5, pp. 2070-2079, 2014.

- [24] R. Wittmann, "Miniaturization Problems in CMOS Technology: Investigation of Doping Profiles and Reliability", *PhD Thesis, Vienna University of Technology*, 2007.

- [25] H. Henry, Radamson et. al., "Miniaturization CMOS", *Micromachines*, vol. 10, no. 5, pp. 1-52, 2019.

- [26] M.S. Phadke, "Quality Engineering Using Robust Design," *Pearson Education Inc. and Dorling Kinderesley Publishing Inc.* 2008.

- [27] S. Rahul, B. Datta, Bhusan Biswal and M. Sankar, "Optimization of Electro-Discharge Machining Responses of Super Alloy Inconel 718: Use of Satisfaction Function Approach Combined with Taguchi Philosophy," *Materials Today: Proceedings*, vol. 5, no. 2, pp. 4376–4383, 2018.

- [28] B. Roozbehani, S.A. Sakaki, M. Shishesaz, N. Abdollahkhani and S. Hamedifar, "Taguchi method approach on catalytic degradation of polyethylene and polypropylene into gasoline," *Clean Technologies and Environmental Policy*, vol. 17, no. 7, pp. 1873–1882, 2017.

- [29] ITRS, International Technology Roadmap Semiconductor, 2013.

- [30] Yiwei Duan et. al., "Low-power consumption organic field-effect transistors," *Journal of Physics: Materials, vol.* 3, no. 1, pp. 1-14, 2020.

- [31] Nor Fareza Kosmani, Fatimah A. Hamid, M. Anas Razali, "Effects of High-k Dielectric Materials on Electrical Performance of Double Gate and Gate-All-Around MOSFET", *International Journal of Integrated Engineering*, vol. 12, no. 2, pp. 81-88, 2020.