# APPENDIX Arduino Based Digital IC Tester

Mohd Adib Bin Sulaiman

Faculty of Electrical Engineering Universiti Teknologi MARA Malaysia 40450 Shah Alam, Selangor, Malaysia mista jebon@yahoo.com

*Abstract*— Nowadays integrated circuits (IC) chip is rapidly growth and become more complexity. The need of devices that can test this IC chip reliable and low cost is very necessary. This paper describes a low cost digital IC tester implemented using the Arduino Mega 2560 microcontroller. The digital IC tester receives keypad information about the chip under test, then the microcontroller will send digital signal to the chip. The resulting chip outputs are then compare with the IC chip expected result to determine whether chip under test is faulty or not.

Keywords-component: transistor-transistor logic (TTL), liquid crystal display (LCD).

## I. INTRODUCTION

Moore's Law (1965), states that the density of transistor and performance of chip will be double for approximately 18 months [1]. The phenomenon known as Moore's Law is then use as benchmark or describing the pace of evolution in the semiconductor world. After 50 years of Moore's Law the technology growth of integrated circuit is still increasing. As the dimension of a transistor shrank, the transistor become smaller, lighter, faster, consumed less power and in most cases was more reliable [2]. These entire elements make the transistor more desirable for any field of application.

The history of semiconductor test technology has been around just about as long as ICs themselves. During mid-1950s at Texas Industries (TI), rows of operators are used to tested transistor. For each transistor it required 10 to 20 different test which leads to slow result and more manpower. By the end of 1958, TI engineers invented a machine call Centralized Automatic Tester (CAT). This machine is capable of testing 2,000 transistors per hour and it is cost effective [3].

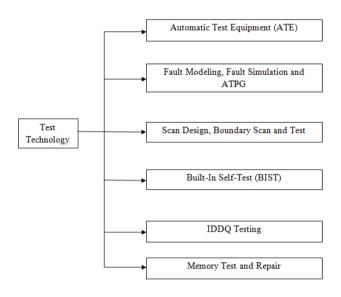

In the five decades of test technology evolution the space limitation has become the major issue. The test technologies development has continue evolving since then. Because of that many testing method is invent in order to prevent this problems. Figure 1 shows some of test technology in past five decades. These technologies have made their appearances early 70s and have been on a continuously evolving curve since then [4]. The test technology shows at figure 1 are describe below.

Figure 1 Highlight of five decades of test technology

# Automatic Test Equipment (ATE)

ATE technology has evolve in line with IC technology and demand in market because it satisfy test throughput, cost and quality demands

# Fault Modeling, Fault Simulation and ATPG

Single stuck at fault model are most well known fault model still in use today. The technology growth has driven the development of efficient fault simulation algorithms and automatic test pattern generation (ATPG) algorithms. These three tools have formed the most fundamental for other test technologies to evolve.

#### Scan Design, Boundary Scan and Test

With increasing circuit complexity and pin number limitation problems. Scan design is the design strategies to overcome this problem and reduce the problem of ATPG for sequential circuit. It first introduces in 1970s. Scan design enables a circuit to have a test mode wherein all memory elements (FFs) of a sequential serially input and output bits of (test) information [5]. Boundary scan form a variant initially developed to accommodate loaded board test [6].

## **Built-In Test Self Test (BIST)**

Commonly discuss in 70s it is the simple method but extremely powerful concept. Basic concept of BIST, it uses the circuitry on the ICs to test the IC itself and it use some form of signature analysis to capture and compact the test results.

# **IDDQ** testing

This test uses power supply current signatures in order to detect good from bad circuits.

#### **Memory Test and Repair**

Memories, particularly embedded have formed a very substantially constituent of modern system on chip. Over the year's specific and sophisticated memory test, diagnosis and repair techniques have been developed.

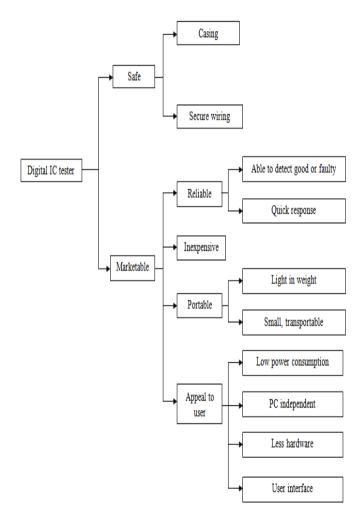

Figure 2 Objective tree of digital IC tester

The objective tree of digital IC tester proposed in this paper shown in figure 2. When designing the IC tester it should be safe for user to use it. The design should be in casing and have secure wiring like the design in [7]. It may not be worth to invest large sum of money into complex IC testers because this IC tester is used in small-scale environment. The purposed IC tester in this paper should be inexpensive and portable because it only used in small-scale environment. Before this inexpensive and portable IC tester have been designs already in paper [8] and [9].

The purposed IC tester should attract the user like have low power consumption, PC independent, less hardware and have user interface. Before this there is design like this described in paper [10]. The main thing when designing the IC tester it should be reliable, mean that it will be able to detect good or faulty chip with quick response. If the IC tester does not have reliable capabilities it's not relevant that the IC tester to used for testing chip. Previous, there are IC tester have reliable capabilities described in paper [11], [12], [13] and [14].

IC manufacturing is rapidly leading to more complex circuit and multi-million chips because of the dramatic improvement of integrated circuit technology. The rapid growth of the IC is expected to increase in the future. With increasing complexity of the IC problems related to IC testing have become more complex and critical. The cost of testing the IC has become major problem of the total cost of electronic production. It predicted that it will soon cost more than to test a transistor than to make it if the main problem of IC testing is not been resolved. IC testing has now become major problems in the semiconductor world and it will need an economic solution with reliable performance.

IC tester is a special device to testing the IC chip. Integrated circuits have three types which are analog integrated circuits, digital integrated circuits and mixed integrated circuits. Thus there are three kinds of tester, which are digital integrated circuits tester [15, 16], analog integrated circuits tester and mixed integrated circuit [17, 18]. The function of tester can be divided into two which are functional test and parametric test. Functional test is to determine the functionality of IC to judge whether their functions fail or not [19]. Parametric test is to determine the parameters of IC to judge whether their parameters meet the design requirement or not [20]. Compare to functional test, the parametric test is very high cost so functional test is widely use in digital IC tester area. In this paper, functional test method is use to test the digital IC.

The digital IC tester proposed in this paper is inexpensive testing device which can test functionality of most TTL and CMOS digital ICs (74 series logic ICs). It can be used for small or medium scale user and provide quick test for the digital ICs. These testers are low power consumption, low cost, less hardware complexity and smaller size makes it unique compare to other IC testers.

#### II. METHODOLOGY

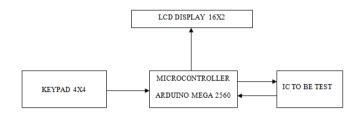

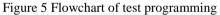

The system flow diagram shows in figure 3. The test system component consist of microcontroller (Arduino Mega 2560), keypad, LCD and IC to be test (ZIF socket). The system used microcontroller in order to identify 74 series logic ICs and can detect faulty IC chips. It identifies by sending digital signal to the IC to be test and then the resulted output is compare with expected result by microcontroller. The test result is then display on the LCD. The main component of this system is microcontroller; it is used for testing computation and controlling the LCD display. To provides good interface to user LCD display and keypad are used in this system.

Figure 3 test system flow diagram

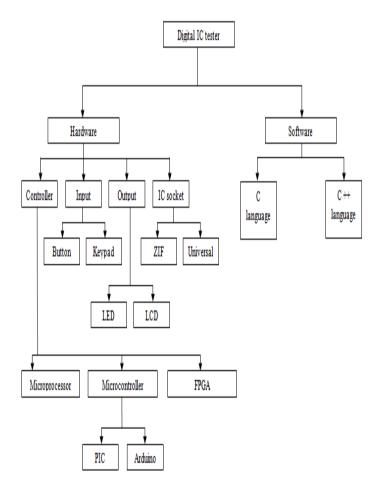

Figure 4 Design selection of IC tester

Before the final design is made design selection must be done first in order to list out what hardware and software most suitable for this proposed digital IC tester. The design selections of proposed digital IC tester are divided into two categories which is hardware and software shows in figure 4. The detail about hardware and software selection described below.

# A. Hardware Design

The designs for hardware are divided into four categories which are controller, input, output and IC socket. The detail of hardware selection of this design described below.

1. Controller

There are three type of controller commonly used in testing area which are microprocessor, microcontroller and field-programmable gate array (FPGA). Microprocessor is not suitable for the controller because hardware complexity and difficult programming environment like the digital IC tester in paper [21]. FPGA controller is much advance and complicated controller. For testing digital IC logic gate this advance controller is not suitable to test the digital IC and it also expensive compare to other controller. Lastly the main choice of the controller for this design which is summarized into two categories PIC and Arduino. Compare to PIC, Arduino is more suitable to use as the main controller of this design because it is inexpensive, reliable and use simple programming environment. Arduino that is used in this design is Arduino Mega 2560. The Arduino Mega 2560 is a microcontroller based on the ATmega2560. ATmega2560 has 256 KB flash memory for storing code (of which 8 KB is used for the boot loader), 8 KB of SRAM and 4 KB of EEPROM.

2. Input

For the input there are two types of hardware possible to use which is button and keypad. In paper [22] the design use button as an interface for the user. The button function is to start the IC testing for the system. For this proposed digital IC tester, keypad is used for interfacing with the user. The function of this keypad is to enter the IC number for the chip under test. Compare to button, keypad is much better interface and easy to program it. Membrane matrix keypad 4x4 is used for this system.

3. Output

Although using LED as the output display for this system is much more simple compare to LCD but using LCD provide better interface with user. The function of the LCD used in the system is to provide test result for each gate of ICs chip that have been tested and the output display when the keypad is pressed. If the LED is used in this system, it is difficult to know what keypad is pressed. So LCD and keypad provide good interfacing for the user.

4. IC socket

Universal type socket is not suitable because when the chip is finishing testing it difficult to pull out the chip out. The chip lead tend to bend or broken off if not handle with care. So ZIF socket is used for IC testing socket to overcome this problem. ZIF socket have a lever or slide, when the slide is pull down the IC chip place in the socket will not damage because the entire IC pin is held by the slider.

B. Software Design

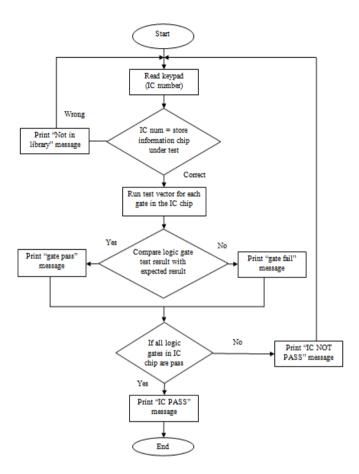

The programming language used in this system is C language because this system used Arduino as the main controller. Arduino used C language that has been simplfy into libraries and use special command. So to programming the Arduino is much easier than using the PIC platform. The flowchart of test program is shown in figure 5. When the system is ON, the microcontroller will read the keypad if there any input parameter. Then, the parameter is compare with the chip information store in the flash memory. The store information will have chip names and specific test vector for the chip to be tested. For example, the chip quad 2 input nand can be stored as "7400" in the program chip information.

In 74 series logic ICs family, every type of ICs have different pin mapping. So in the programming there six set of structure with different input and output test vector. Because of test socket connected series, there is floating input and output when the port of microcontroller is not used. So, the ports are put in calling function in order to avoid this problem. It is used when desired test vector is call in the programming. Other reason the port is put in calling function because the port is reused again for testing in different type IC. By recycling the port, port used in this system can be minimized.

When the input IC number is equal to IC chip information store in the flash memory, the microcontroller will send desired digital signal to the chip input under test and the output of chip under test will be read by the microcontroller. The test result for every logic gates that have been tested in the IC chip are compared with the expected result. If the gate is ok LCD will print "gate pass" and if not the LCD will print "gate fail". And then the test result of all logic gate are then compared, if the entire logic gate is working the chip is not faulty. The LCD will print "IC PASS" and some of the logic gate is not working the LCD will print "IC NOT PASS".

In the programming system there is six set of IC test because there are six types pin mapping configuration. Let say the first set of test is already done, the second set of test will fail if IC test is run. This happen because the input of first test is already stored in flash memory. The second set of test can only be done if the reset button on the microcontroller is push, it mean that it can only running if the flash memory is wipe out by resetting the board. So to solve the problem, software reset called "watchdog timer" is put after the test result is print on the LCD. So after test is complete it will wipe out the information store in the flash memory.

#### III. RESULT AND DISCUSSION

The prototype of IC tester proposed in this paper is shown in figure 7. Table 1 shows the basic information chip under test that can be tested with this IC tester. To check whether this system is reliable, set of test have been made for every chip that can be tested. After that faulty coverage is record for each chip that has been tested in Table 2.

Table 1 Basic information chip under test

| Туре | Function          |  |  |

|------|-------------------|--|--|

| 7400 | Quad 2-input NAND |  |  |

| 7408 | Quad 2-input AND  |  |  |

| 7432 | Quad 2-input OR   |  |  |

| 7486 | Quad 2-input EX-OR  |  |  |

|------|---------------------|--|--|

| 7402 | Quad 2-input NOR    |  |  |

| 7410 | Triple 3-input NAND |  |  |

| 7411 | Triple 3-input AND  |  |  |

| 7427 | Triple 3-input NOR  |  |  |

| 7420 | Dual 4-input NAND   |  |  |

| 7421 | Dual 4-input AND    |  |  |

| 7430 | 8-input NAND gate   |  |  |

| 7404 | Hex NOT             |  |  |

Table 2 Test Result IC under Test

| Туре | Total | Faults | Flts det | %Flts |

|------|-------|--------|----------|-------|

|      |       |        |          | cov.  |

| 7400 | 10    | 5      | 5        | 100   |

| 7408 | 10    | 5      | 5        | 100   |

| 7432 | 10    | 5      | 5        | 100   |

| 7486 | 10    | 5      | 5        | 100   |

| 7410 | 10    | 5      | 5        | 100   |

| 7411 | 10    | 5      | 5        | 100   |

| 7427 | 10    | 5      | 5        | 100   |

| 7420 | 10    | 5      | 5        | 100   |

| 7421 | 10    | 5      | 5        | 100   |

| 7430 | 10    | 5      | 5        | 100   |

| 7404 | 10    | 5      | 5        | 100   |

Figure 6 Prototype of Arduino Based IC Tester

Table 2 shown the test result for chip under test which include type of IC, total indicates the total number of chip being tested, faulty indicates the number of IC chips are faulty, flts det mean how many of faulty chips is detected and flts cov indicates the faults coverage of testing. From the result, it can conclude that this IC tester is reliable and effective to detect faulty chip because the test result shows that this tester have 100% of faults coverage.

#### IV. CONCLUSION

Based from the test result, this proposed digital IC tester has successfully tested a variety of 74 series logic ICs without any problem by achieving 100% fault coverage for all chips under test. From the test result its proof that this IC tester is reliable and effective for detecting faulty logic gate ICs. The IC to be test can be expand to 4000 series logic ICs by slightly modification the code and hardware.

The digital IC tester design aim to give "PASS" or "NOT PASS" logic report on the IC being tested. It is beyond capable of this tester to attempt to measure ICs analogue operational parameter and compare with the ICs specification. Although the Arduino Mega 2560 have analog and digital port, perhaps the author can redesign the tester so it can capable to test other 74 series logic ICs such as decoder and counter ICs.

#### ACKNOWLEDGMENT

The author would like to thank UniversitiTeknologi MARA (UiTM) Malaysia, Syed Abdul Mutalib Al Junid for all the guidance, support and advice provided to me throughout the final year project.

#### REFERENCES

[1, 2] Chris A. Mack, 2011, Fifty years of Moore's Law, IEE Transaction on Semiconductor Manufacturing Vol. 24, no 2, may 2011.

[3]http://www.ti.com/corp/docs/company/history/timeline/semicon/1950/docs/58cat\_machine.htm

[4-6] Andre Ivanov, 2007, From (Integrated) Circuits to Systems of System on Chip in Five Decades : How did and will IC Test Technologies keep up, Department of Electrical and Computer Engineering, University of British Columbia.

[7, 9, 10, 11, 22] Mirza Shoaib Ahmed, Iqbal Muhammad Umair and Kashif Mehboob, 2005, Microcontroller Based IC Tester.

[8, 12] Joe Farr, Digital IC Tester, October 2002, EPE Magazine.

[13, 19, 20] K Aijun Zhu, 2012, Test System for Digital General-Pupose Integrated Chip, Advanced Material Research Vols. 490-495 (2012) pp 2969-2930.

[14, 21] Gary L. West, H. Troy Nagle JR., Victor P. Nelsen, A Microcomputer-Controlled Testing System for Digital Integrated Circuits, IEEE Transactions On Industrial Electronics And Control Instrumentation, Vol. Ieci-27, No. 4, Nov. 1980.

[15] Thibeault, C. Improving digital IC testing with analog circuits. *4th International IEEE North-East Workshop on Circuits and System.* 2006; p 285-288.

[16] Uiu Güler, Ulkühan. Ergün, Salih; Dündar, Günhan. A digital IC random number generator with logic gates only. 2010 IEEE

[17] Gong, Yinshui Li, Huiyun. FPGA based testing method to improve digital IC testability. *Applied Mechanics and Materials.* 2012; p 3920-3923.[18] Bhatia, Anuj. Hofmeister, James P. Judkins, Justin. Goodman, Doug.

Advanced testing and prognostics of ball grid array components with a