# ELECTRICAL ANALYSIS OF SI<sub>3</sub>N<sub>4</sub> CAPPING LAYER AND SOI TECHNOLOGY IN SUB-65 nm CMOS

# SYED MUHAMAD FIRDAUZ BIN SYED ADRUS

This thesis is presented in partial fulfilment for the award of the

**Bachelor of Engineering (Hons) Electrical**

NOVEMBER 2008

BACHELOR OF ENGINEERING (HONS) ELECTRICAL FACULTY OF ELECTRICAL ENGINEERING UNIVERSITI TEKNOLOGI MARA PULAU PINANG

### ACKNOWLEDGEMENTS

Purity belongs to Allah S.W.T, God of the entire world and hereafter, the gracious, the merciful of giving me the strength and patience to complete this final project successfully. All the difficulties that were faces make me realize that it was not that easy to become an excellent student in this university.

Without the help and supports from others individuals, it is impossible for me to complete this project successfully. Very great thanks to my supervisor Mr Hanapiah Bin Abdullah who always provides good supervision, encouragement and critic. I am truly indebt with all the helps that he provide for me during completing this final project.

My thank also go to Puan Rosfariza Radzali and Puan Sharifah Saliha who are always give suggestion, idea and help me in completing this final project. Their contributions really mean a lot to me to form better in my final project thesis.

Thank you to my beloved parent and my family that support all through the process of completing this final project thesis. They have been a wonderful source of support, inspiration and encouragement throughout my education, and they deserve much credit for where I am today.

Finally, to all persons that involve directly and indirectly with full willingness of contributing their efforts, time, energy and idea, helping me completed this thesis. There are no exact words that can express my feeling of gratitude toward them except thank you.

#### ABSTRACT

Starting at the 65nm node, stress engineering to improve performance of transistors has been a major industry focus. An intrinsic stress source, shallow trench isolation (STI) has not been fully utilized up to now for circuit performance improvement. In this paper, two methods have been used on 65nm CMOS that combines with detailed placement and active-layer fill insertion to analyze for performance improvement.

First method is to investigate electrical characteristics for 65 nm NMOS by using  $Si_3N_4$  capping layer for three different layers thickness (30 nm, 60 nm and 100 nm. Second method is using 0.4  $\mu$ m thickness of Silicon-on-Insulator (SOI) Technology for 65 nm PMOS. The performance of the devices is analyzed by focusing on the electrical characteristics of Id– Vd and Id–Vg curves for both capping layer and SOI technology.

The results shows that, thicker capping layer thickness offer higher stress in CMOS, this improves the acceleration of electron mobility and increases the drive saturation current in NMOS of about 14%. Meanwhile, by implemented SOI technology shows improvement in threshold voltage (with decrement of 8.5%) and drain saturation current (with increment of 4.7%). The fabrication process simulation and electrical characteristic was simulated by using SILVACO TCAD ATHENA and ATLAS simulator.

# **TABLE OF CONTENTS**

| ACKNOWLEDGEMENTS                     |                                                                 |                                                       | v    |

|--------------------------------------|-----------------------------------------------------------------|-------------------------------------------------------|------|

| ABS                                  | TRACT                                                           |                                                       | vi   |

| TABLE OF CONTENTS<br>LIST OF FIGURES |                                                                 |                                                       | vii  |

|                                      |                                                                 |                                                       | xi   |

| LIST                                 | <b>OF TA</b>                                                    | BLE                                                   | xiii |

| ABB                                  | REVIA                                                           | TIONS                                                 | xiv  |

| CHA                                  | PTER 1                                                          | L                                                     |      |

| INTI                                 | RODUC                                                           | TION                                                  | 1    |

| 1.0                                  | Chapt                                                           | er Overview                                           | 1    |

| 1.1                                  | Background                                                      |                                                       | 1    |

|                                      | 1.1.1                                                           | Technology of 65 nm CMOS                              | 2    |

| 1.2                                  | Objec                                                           | tive of the project                                   | 5    |

| 1.3                                  | Scope                                                           | e of Work                                             | 6    |

| 1.4                                  | Overv                                                           | riew                                                  | 7    |

| CHA                                  | PTER 2                                                          | 2                                                     |      |

| LITI                                 | ERATUI                                                          | RE REVIEW                                             | 8    |

| 2.0                                  | Chapt                                                           | er Overview                                           | 8    |

| 2.1                                  | Silicon Nitride (Si <sub>3</sub> N <sub>4</sub> ) Capping Layer |                                                       | 8    |

| 2.2                                  | SOI Technology                                                  |                                                       | 10   |

|                                      | 2.2.1                                                           | Basic Mainstream of SOI Technology                    | 13   |

|                                      |                                                                 | 2.2.1.1 SIMOX                                         | 13   |

|                                      |                                                                 | 2.2.1.2 BESOI                                         | 13   |

|                                      | 2.2.2                                                           | SOI Device Description and Modeling Issues            | 14   |

|                                      |                                                                 | 2.2.2.1 Thick-film (Partially-depleted) PD-SOI device | 14   |

|                                      |                                                                 | 2.2.2.2 Thin-film (Fully-depleted) FD-SOI device      | 15   |

# **CHAPTER 1**

## **INTRODUCTION**

#### 1.0 Chapter Overview

This chapter describes the objective of this project, brief explanation process involved, scope of work that have been done in completing this project and overall chapter in this project.

#### 1.1 Background

CMOS are becoming very popular devices nowadays. The widely used CMOS has forced the industries to compete among themselves in order to produce the best performance of CMOS. The technologies and demands have caused the reducing on the gate length of the CMOS from 130nm to 65nm. Recently, industries have begun shipping products built on 65nm technology.

Device structure and fabrication play an important role in determining the overall effectiveness, performance, and cost of a logic chip. Logic devices are attaining smaller process geometries and higher levels of integration. 65nm processes offer designers the capability to integrate more complex functionality at higher performance on a single chip. However, the smaller geometry gates do not come without a cost, and an increasingly dominant one is power dissipation [14].

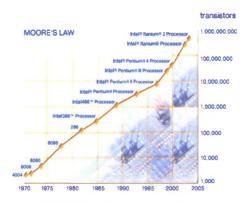

Figure 1.1 Moore's Law