## ELECTRICAL ENGINEERING FACULTY OF UNIVERSITY TECHNOLOGY MARA

# FINAL REPORT FOR DIPLOMA PROJECT (KEU 380)

**DATE: 15 APRIL 2000**

PROJECT TITLE: LAMP TIMER

PREPARED BY:

AZIZEY B. MOKHTAR (KE-11) 97033878 AZARUL HISHAM B. ALIAS (KE-11) 97033846

SUPERVISOR: Miss. WAN SALHA Bt. SAIDON

#### **ACKNOWLEDGMENTS**

First of all with the name of Allah S W T the most gracious and merciful, and to our prophet Muhammad S.A.W. Thanks to Allah S.W.T for giving us opportunity to complete this project successfully. Lamp timer was one of the most familiar and the best project in electronics that we have found out from many multimedia and other references. This project initially is not very difficult since we know how it being able and how the system function be operated. We would like to express our deep sense of gratitude and appreciation to our project advisor Miss Wan Salha Saidon, Miss Taniza Tajuddin, our co-ordinator Leader Madam Nooritawati Tahir for the consistent help and guidance as well as prevision of their valuable time, encourage and patient during the period to complete this project. We are very grateful to them and we will never forget for everything what they have done to us. Only Allah S.W.T could pay back their kindness and we will appreciate it till the rest of our life. We also want to thanks to all our electronic lectures because from them we got all the good ideas for our project. Finally, this expression also goes to all our friends that willing to help us while doing our project. Last but not least, all which are good come from Allah S.W.T and all which bad are come from us.

## **ASTRACT**

A timed switch uses a 555 oscillator/timer wired to operate in the astable mode. The timer supplies a positive pulse to the clock input of 79193 4-bit binary up/down count every five minutes. Because the 74193 is set to operate in the count-down mode, the output of the 555 is connected to thee count-down input of the 74193. As the binary counter is reset, it starts counting at nine and counts down to zero with each clock pulse. When the counter hits zero, the output from the 74193 goes low, turning off the relay and the light. The light can be turned back on by pressing the reset button again.

KEU 380

## **CONTENTS:**

| Abstract                        | <u>Page No.</u><br>(i) |

|---------------------------------|------------------------|

| 1.0 Introduction                | 1                      |

| 2.0 System design Consideration | 2                      |

| 2 l Stage l                     | 2                      |

| 2.2 Stage II                    | 5                      |

| 2.3 Stage III                   | 8                      |

| 2.4 Stage IV                    | 12                     |

| 2.5 Stage V                     | 13                     |

| 3.0 Simulation                  | 14                     |

| 3 1 Circuit                     | 15                     |

| 4.0 Problem Identification      | 17                     |

| 5.0 Work Planning               | 18                     |

| 6.0 The cost the project        | 19                     |

| 7.0 Conclusion                  | 20                     |

| 8.0 References                  | 21                     |

| 9.0 Appendices                  |                        |

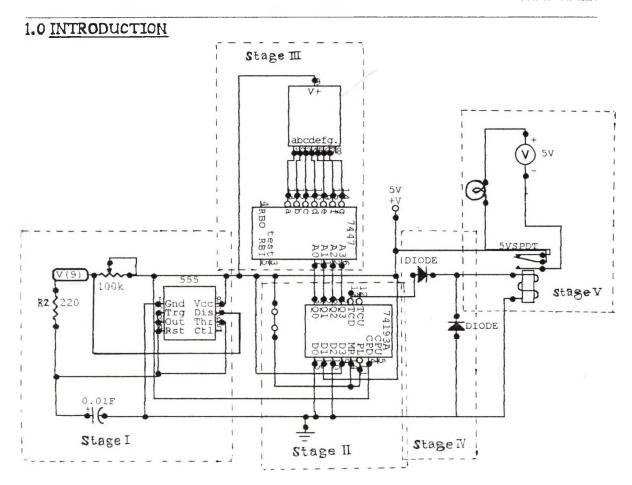

A timed switch uses a 555 oscillator / timer wired to operate in the astable mode. When power is first turned 'ON' the capacitor is discharged, which place 0V at pin 2 forcing the output HIGH. With the output HIGH, the discharge transistor in 555 is open which allows the capacitor voltage exceeds 2/3 Vcc, it forcing the output LOW. With output LOW the transistor shorts pin 7 to ground, which discharge again the capacitor via R2. The cycle repeats with the capacitor charging up to 2/3 Vcc, then discharging down to 1/3 Vcc continuously. The output of the timer will supplies clock pulse and connected to the clock input Cpo of a 74193 - 4 bit binary Up/Down. The 74193 is set to operate in the count-down mode. The binary output count is taken from Q0 to Q3 which are output from four internal J-K flip-flops and connnected to 7447-Common-Anode Decoder/LED driver. Basically, the 7447 has a 4-bit BCD input and seven individual active -LOW outputs (one for each LED segment). The Master Reset (MR) is an active -HIGH Reset for resetting the Q output to zero. As the binary counter is reset, it starts to counting at nine and counts down to zero with each clock pulse. When the counter hits zero, the output from the 74193 goes LOW, turning 'OFF' the relay and light. The light can be turned back 'ON' by pressing the button again. For the furthermore information since we studied how does the circuit function and how does the operation be able, we have devide this circuit into five stage as we will explain more detail in the System Design Consideration

KEU 380