# CHARACTERIZATION OF MULTILEVEL INTERCONNECT CAPACITANCE FOR 0.35µm CMOS TECHNOLOGY

Thesis submitted to the Faculty of Electrical Engineering, Universiti Teknologi MARA in fulfilment of the requirement for the Degree of Bachelor of Engineering

FAIZUL BIN OTHMAN FACULTY OF ELECTRICAL ENGINEERING UNIVERSITI TEKNOLOGI MARA 40450 SHAH ALAM SELANGOR DARUL EHSAN

**MAY 2007**

### ACKNOWLEDGEMENT

All praise to Allah who has given me the strength and ability to complete this thesis.

I am grateful to Mr Abdul Hadi bin Abdul Razak for the supervision and guidance throughout the research. I am also thankful to Mr Rofei Mat Husin of MIMOS Berhad for providing insight to research approach and support given throughout the research. I am indebted to MIMOS Berhad for allowing academic research to be implemented in highly sensitive, expensive and confidential environment.

On a personal note, I would like to thank my parents for their encouragement and continuous support for me during my studies in Universiti Teknologi MARA.

Last but not least, thank you to my friends who have helped me to complete the research in various ways.

### ABSTRACT

This thesis presents a methodology for an interconnect capacitance characterization for  $0.35\mu$ m CMOS technology with three-level metals. The purpose of this work is to generate a capacitance table for the new MIMOS  $0.35\mu$ m CMOS process and compare with the previous back end process. The generated table is based on simulation results from Raphael field solver simulation tools. Parasitic capacitance database is created and capacitance rules file are generated for parasitic extraction using layout parameter extraction (LPE) tools, Calibre xRC. The methodology starts with plate capacitor measurement, followed by field solver simulation, and finally data verification. This methodology proves sufficiently accurate enough in technology library characterization for MIMOS  $0.35\mu$ m CMOS process. The comparison of the process shows that the interconnect capacitance from the new process increased due to the smaller design rules implemented.

## TABLE OF CONTENT

### CONTENTS

| ACKNOWLEI        | GEMEN                                           | VT                                           | i          |

|------------------|-------------------------------------------------|----------------------------------------------|------------|

| ABSTRACT         |                                                 |                                              | ii         |

| TABLE OF CONTENT |                                                 |                                              | iii        |

| LIST OF FIGU     | IRES                                            |                                              | <b>v</b> . |

| LIST OF TAB      | LES                                             |                                              | vi         |

| LIST OF ABB      | REVIAT                                          | IONS                                         | vii        |

| CHAPTER 1        | INTRO                                           | DUCTION                                      |            |

| 1.1              | Evolutio                                        | volution of Interconnect for CMOS Technology |            |

| 1.2              | Researc                                         | Research Objectives                          |            |

| 1.3              | Structur                                        | re of Thesis                                 | 3          |

| CHAPTER 2        | LITER                                           | ATURE REVIEW                                 |            |

| 2.1              | Back-End Processing                             |                                              | 6          |

| 2.2              | The Need for Multilevel Interconnect Technology |                                              | 8          |

|                  | 2.2.1                                           | Functional Density                           | 8          |

|                  | 2.2.2                                           | Propagation Delay                            | 8          |

|                  | 2.2.3                                           | Wafer-Scale Integration                      | 9          |

|                  | 2.2.4                                           | Cost                                         | 10         |

| 2.3              | Capacitors and Dielectrics                      |                                              | 10         |

|                  | 2.3.1                                           | The Capacitance of a Capacitor               | 10         |

|                  | 2.3.2                                           | The Dielectric Constant                      | 11         |

|                  | 2.3.3                                           | The Capacitance of Parallel Plate Capacitor  | 12         |

| 2.4              | Capacitance Model                               |                                              | 13         |

|                  | 2.4.1                                           | Area Capacitance                             | 15         |

|                  | 2.4.2                                           | Coupling Capacitance                         | 16         |

|                  | 2.4.3                                           | Fringe Capacitance                           | 17         |

| CHAPTER 3        | CHARACTERIZATION METHODOLOGY                    |                                              |            |

| 3.1              | Project Flow                                    |                                              | 20         |

| 3.2              | Capacitor                                       |                                              | 21         |

|                  | 3.2.1                                           | Plate Capacitor Test Structures              | 21         |

|                  | 3.2.2                                           | Electrical Measurement                       | 22         |

|                  | 3.2.3                                           | Dielectric Thickness Measurement             | 22         |

|                  |                                                 |                                              |            |

### **CHAPTER 1**

### **INTRODUCTION**

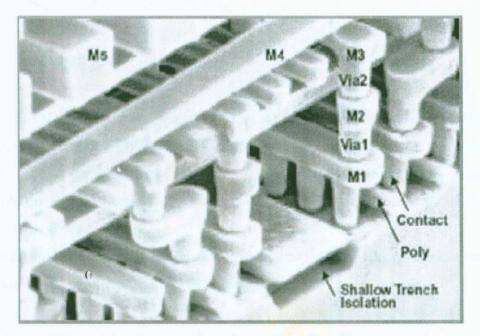

In order to construct a Very Large Scale Integration (VLSI) circuits, it is necessary to fabricate many active devices on a single wafer. Initially, each of the devices must be isolated from the others, but later in the fabrication process specific devices must be interconnected in order to realize the desired circuit function [1]. Nowadays, in the VLSI circuits, the density of the circuit steadily increases as the transistor gate length downscaled with each new generation. Therefore, it will condense the circuit with millions of logic gates and several kilometers of wire. Interconnect is a process of wiring the devices on the wafer during the back-end process, as it becomes multilevel and more complex, it will greatly affect the performance of the circuits. Under this circumstances, accurate characterization and simulation of the multilevel interconnect are crucial to predict the performance of the circuit. For this research effort, the research work is implemented in Malaysian Institute of Microelectronic System (MIMOS) Berhad.

Figure 1.1: Cross section views of multilevel interconnect.