### SIMULATION OF DRAIN INDUCED BARRIER LOWERING (DIBL) IN METAL OXIDE SEMICONDUCTOR FIELD EFFECT TRANSISTOR (MOSFET)

#### FLORENCE ELNA ANAK NELSON

# THIS THESIS IS SUBMITTED IN PART FULFILLMENT OF THE REQUIREMENT FOR THE DEGREE BACHELOR OF ENGINEERING (HONS.) ELECTRONIC

# FACULTY OF ELECTRICAL ENGINEERING UNIVERSITY TEKNOLOGI MARA MALAYSIA

#### **ACKNOWLEDGEMENT**

First of all, I want to thank God for giving me blessings and I am very grateful that I am able to finish my final year project successfully and on time. The research presented in this dissertation could never be done without many support and cooperation of people directly or indirectly.

Next, I would like to express my gratitude to my project supervisor, Mr. Azrif Bin Manut for giving me the opportunity to learn under his guidance. Thank you for the time, the support, ideas and knowledge that he gave to me throughout this project, starting from my final project one (FYP1) until the end of my final project two (FYP2). All of these are a very memorable experience for me. Without his guidance and persistent help this dissertation would not have been possible.

In addition, my gratitude also goes to the panels, Dr. Mohd Hafiz and Dr. Zulfakri for the comments they gave me during the presentation. I really appreciate their comments. Also, thanks to Mr. Mohd Rofei from MIMOS Berhad for helping me by explaining and giving me more information related to this project.

I also would like to thank my friends and family members for always being there for me and give me huge supports in many ways in completing my final year project. Once again, thank you everyone for everything. Only God can repay your kindness, supports and sacrifices.

#### **ABSTRACT**

This paper shows Simulation of Drain Induced Barrier Lowering (DIBL) in Metal Oxide Semiconductor Field Effect Transistor (MOSFET)". The research and study on this is investigated. Using software from SILVACO International, the simulation of the N-channel metal oxide semiconductor (NMOS) can be studied and the study is about DIBL due to short channel. SILVACO technology computer-aided design (TCAD) software is use to do the simulation and to obtain all the results needed. The virtually fabrication of NMOS is done using ATHENA module meanwhile for electrical characterizations of NMOS is done using ATLAS module. Using this software, the structure of MOSFET and I-V curve can be plotted through the TONYPLOT. In this study, the drain voltage, V<sub>D</sub> and channel length, L act as the main roles in the results. Therefore, to see the role of drain voltage on DIBL, five different values of drain voltage, V<sub>D</sub> which are 0.1 V, 0.2 V, 0.3 V, 0.4 V and 0.5 V are used. Meanwhile, for channel length, L, the values used are 0.20 µm, 0.30 µm, 0.40 µm and 0.50 µm. From drain current, I<sub>D</sub> versus gate voltage, V<sub>G</sub> (I-V) curve, the value of DIBL is obtained and analyzed to complete the analysis of DIBL. When the drain voltage, V<sub>D</sub> increasing, the potential barrier in the channel decreasing which leads to DIBL. As the voltage drain, V<sub>D</sub> is increasing, and the barrier height is decreasing while the drain current, ID is increasing. This project do achieved the objectives of the project.

Keywords-DIBL, SILVACO TCAD, NMOS, TONYPLOT

### TABLES OF CONTENTS

|                                            | PAGE |

|--------------------------------------------|------|

| DECLARATION                                | i    |

| ACKNOWLEGMENT                              | ii   |

| ABSTRACT                                   | iii  |

| TABLES OF CONTENTS                         | iv   |

| LIST OF TABLES                             | vi   |

| LIST OF FIGURES                            | vii  |

| LIST OF SYMBOLS AND ABBREVIATIONS          | viii |

|                                            |      |

| CHAPTER 1: INTRODUCTION                    |      |

| 1.1 INTRODUCTION                           | 1    |

| 1.2 BACKGROUND OF STUDY                    | 7    |

| 1.3 PROBLEM STATEMENTS                     | 8    |

| 1.4 OBJECTIVES                             | 8    |

| 1.5 SCOPE OF WORKS AND LIMITATION OF STUDY | 9    |

| 1.6 SIGNIFICANT OF STUDY                   | 9    |

| 1.7 THESIS ORGANIZATION                    | 10   |

|                                            |      |

| CHAPTER 2: LITERATURE REVIEW               |      |

| 2.1 SHORT CHANNEL EFFECT                   | 11   |

#### **CHAPTER 1**

#### **INTRODUCTION**

#### 1.1 INTRODUCTION

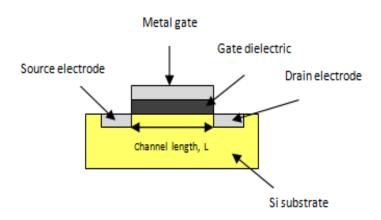

MOSFET is a device which is used to amplify or to switch any kind of electronic signals. Nowadays, we can see that MOSFET technology is one of the most commonly used semiconductor technique, and had become one of the elements in the integrated circuit technology. The power consumptions in integrated circuits can be reduced as MOSFET's has good performance which enables the reduction. A MOSFET has two regions which are mainly named as the source and drain. Both regions are heavily doped and these are implanted in a substrate, which is doped the other way. The current will flow at the gap between the source and drain regions, which spans the substrate. A layer of insulating oxide is placed over this gap, which is well known as the channel. Moreover, on top of that is a gate contact and it is usually made of polysilicon. Figure 1.1 shows the MOSFET structure.

Figure 1.1: MOSFET Structure