# DESIGNING CLOCK GENERATOR AND BCD COUNTER FOR A FREQUENCY COUNTER USING VHDL

Industrial Project Thesis is presented in partial fulfillment for the award of the Bachelor of the Electrical Engineering (Honors)

UNIVERSITI TEKNOLOGI MARA

MOHD FIRDAUS BIN AHMAD

Faculty of Electrical Engineering

UNIVERSITI TEKNOLOGI MARA

40450 Shah Alam, Selangor

## ACKNOWLEDGEMENT

I would like to convey my million thanks to my most respected supervisor Associate Professor Zulkifli Abd. Majid, for him priceless assistance, guidance and support throughout the development of the project. I would also like to express my utmost gratitude to all who have been involved directly or indirectly. May Almighty Allah s.w.t bless and reward them for their generosity.

### **ABSTRACT**

This paper presents a development of a frequency counter using VHDL under Xilinx environment. This frequency counter is based on the premise of counting the incoming known frequency's rising edge for digital signal as a predetermined fixed amount of time, or GATE. The circuit is partitioned in two sequences individual circuit namely as Clock Generator and BCD Counter. The sub circuits for clock generator are Oscillator 4 (OSC4) and counters according to the chosen frequency generated. The circuit for BCD Counter is a main circuit. There are three types of modelling used as an existing method such as behavioural, structural and data flow. Other modelling technique that is also considered is the state machine as an additional method which is coded using VHDL where the results are observable in form of timing diagrams.

# TABLE OF CONTENTS

| DECLARA                                                                                        | ATION       |                     |                          | i                                 |         |              |  |  |      |

|------------------------------------------------------------------------------------------------|-------------|---------------------|--------------------------|-----------------------------------|---------|--------------|--|--|------|

| ACKNOWLEDGEMENT ABSTRACT TABLE OF CONTENTS LIST OF FIGURES LIST OF TABLES LIST OF ABBREVIATION |             |                     |                          | ii<br>iii<br>iv<br>vii<br>x<br>xi |         |              |  |  |      |

|                                                                                                |             |                     |                          |                                   |         |              |  |  |      |

|                                                                                                |             |                     |                          |                                   | CHAPTER |              |  |  | PAGE |

|                                                                                                |             |                     |                          |                                   |         |              |  |  |      |

|                                                                                                |             |                     |                          |                                   | 1       | INTRODUCTION |  |  |      |

|                                                                                                |             |                     |                          |                                   |         |              |  |  |      |

|                                                                                                | 1.1         | Introduction        |                          | 1                                 |         |              |  |  |      |

|                                                                                                |             | 1.1.1 Cour          | nter at Rising Edge      | 1                                 |         |              |  |  |      |

|                                                                                                |             | 1.1.2 The           | VHDL Standard            | 2                                 |         |              |  |  |      |

|                                                                                                |             | 1.1.2               | 1 Why use VHDL?          | 3                                 |         |              |  |  |      |

|                                                                                                |             | 1.1.3 Cond          | cept of VHDL Programming | 4                                 |         |              |  |  |      |

|                                                                                                | 1.2         | .3 Scope of Project |                          | 5                                 |         |              |  |  |      |

|                                                                                                | 1.3         |                     |                          | 5                                 |         |              |  |  |      |

|                                                                                                | 1.4         |                     |                          | 5                                 |         |              |  |  |      |

|                                                                                                | 1.5         | Organization        | n of the Thesis          | 6                                 |         |              |  |  |      |

|                                                                                                |             |                     |                          |                                   |         |              |  |  |      |

| 2                                                                                              | METHODOLOGY |                     |                          |                                   |         |              |  |  |      |

|                                                                                                |             |                     |                          |                                   |         |              |  |  |      |

|                                                                                                | 2.1         | .1 Introduction     |                          | 8                                 |         |              |  |  |      |

|                                                                                                | 2.2         | Designs with        | h Xilinx Foundation      | 9                                 |         |              |  |  |      |

|                                                                                                |             | 2.2.1 Desi          | gn Manager               | 10                                |         |              |  |  |      |

|                                                                                                |             | 2.2.2 New           | Project                  | 10                                |         |              |  |  |      |

#### **CHAPTER 1**

#### INTRODUCTION

#### 1.1 Introduction

The main purpose of this project is to design two major circuits namely Clock Generator and BCD Counter. The Clock Generator circuit comprises of sub circuits, the mode counter and the oscillator (in the oscillator, fix frequencies are chosen to produce desired frequencies). As for the BCD counter, the basic element includes the block for conversion for BCD to 7-segment in the frequency counter. All the components required were coded using VHDL programming under Xilinx environment.

#### 1.1.1 Counter at Rising Edge

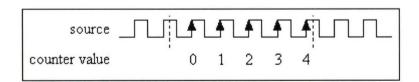

One potential use for counters is to measure the period, or the length of time between successive rising edges, of an incoming signal. A known frequency, usually an internal clock, is used as a reference. The counter starts counting at a rising edge, which is user-configurable, and stops counting at its successive edge [1]. As in Figure 1.1 the pulse period is the number of counts between rising edges divided by the number of counts expected in one second (frequency of the known clock), that is, period = counts / frequency [1] as in Figure 1.2 assume period T = 1.

Figure 1.1: Frequency rising edge