University Publication Centre (UPENA)

# Academic Journal UiTM Pulau Pinang

Volume 6, Number 1

June 2010

ISSN 1675-7939

Organic Semiconductor Characterization Using Linear Combination of Atomic Orbital (LCAO)

Ahmad Nazib Alias Zubainun Mohamed Zabidi Intan Syaffinazzilla Zaine Muhd Zu Azhan Yahya

> N. A. Zubir N. C. Radzi

A. F. Ismail M. Y. Laili

Lim Jit Kheng

Feasibility Study of Pineapple (Ananas cosomus) Leaf Fibres (PALFs) for Cellulosic Microfiltration Membrane

Systematic Statistical Approaches in Classifying Physical Properties of Soft Marine Clay Lim Jit Kheng Ng Set Foong Mohamad Razip Selamat Eric Goh Kok Hoe

Using Intraclass Correlation Coefficient and Bartlett Test Statistic to Identify Soil Layer Boundaries

Fabrication and Characterization of 0.24 Micron CMOS Device by Using Simulation Ng Set Foong Mohamad Razip Selamat Eric Goh Kok Hoe

Nazirah Mohamat Kasim Rosfariza Radzali Ahmad Puad Ismail

VHDL and Computer Aided Design (CAD) Tool Teaching Aid for Future Engineers

Nor Fadzilah Mokhtar Afaf Rozan Mohd Radzol Nazirah Mohamat Kasim Noor Azila Ismail Suzana Ab. Rahim

#### EDITORIAL BOARD **ESTEEM VOLUME 6, NUMBER 1, 2010** Universiti Teknologi MARA (UiTM), Pulau Pinang ENGINEERING

#### **ADVISORS**

Dato' Prof. Ir. Dr. Sahol Hamid Abu Bakar, FASc Assoc. Prof. Mohd Zaki Abdullah

#### PANEL OF REVIEWERS

Prof. Ir. Dr. Zainab Mohamed (*Universiti Teknologi MARA*) Dr. Junita Mohamad Saleh (Universiti Sains Malaysia) Dr. Robert Mikhail Savory (*Universiti Teknologi MARA*) Assoc. Prof. Dr. Mohd Dani Baba (Universiti Teknologi MARA)

#### CHIEF EDITOR

Rasaya Marimuthu

MANAGING EDITOR

Lim Teck Heng

#### LANGUAGE EDITORS

Aznizah Hussin Muriatul Kusmah Musa Noor Laili Mohd Yusof

Rofiza Aboo Bakar Yeoh Guan Joo

Copyright © 2010 UiTM, Pulau Pinang

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or any means, electronic, mechanical, photocopying, recording or otherwise, without prior permission, in writing, from the publisher.

Esteem Academic Journal is jointly published by the Universiti Teknologi MARA, Pulau Pinang and University Publication Centre (UPENA), Universiti Teknologi MARA, 40450 Shah Alam, Selangor, Malaysia.

The views, opinions and technical recommendations expressed by the contributors and authors are entirely their own and do not necessarily reflect the views of the editors, the Faculty or the University.

# **ESTEEM** Academic Journal UiTM Pulau Pinang

| Vo | lume 6, Number 1                                                                                                                                              | June 2010 | ISSN 1675-7939 |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------------|

|    | Foreword                                                                                                                                                      |           | iii            |

| 1. | Organic Semiconductor Char<br>Combination of Atomic Orbi<br>Ahmad Nazib Alias<br>Zubainun Mohamed Zabidi<br>Intan Syaffinazzilla Zaine<br>Muhd Zu Azhan Yahya | 0         | 1              |

| 2. | Feasibility Study of Pineapp<br>Fibres (PALFs) for Cellulosic<br>N. A. Zubir<br>N. C. Radzi<br>A. F. Ismail<br>M. Y. Laili                                    |           | 15             |

| 3. | Systematic Statistical Approa<br>Properties of Soft Marine Cla<br>Lim Jit Kheng<br>Ng Set Foong<br>Mohamad Razip Selamat<br>Eric Goh Kok Hoe                  |           | 27             |

| 4. | Using Intraclass Correlation<br>Statistic to Identify Soil Laye<br>Lim Jit Kheng<br>Ng Set Foong<br>Mohamad Razip Selamat<br>Eric Goh Kok Hoe                 |           | 53             |

5. Fabrication and Characterization of 0.24 Micron CMOS

Device by Using Simulation 73

Nazirah Mohamat Kasim

Rosfariza Radzali

Ahmad Puad Ismail

85

#### VHDL and Computer Aided Design (CAD) Tool Teaching Aid for Future Engineers Nor Fadzilah Mokhtar Afaf Rozan Mohd Radzol Nazirah Mohamat Kasim Noor Azila Ismail Suzana Ab, Rahim

#### Foreword

It is indeed a proud moment for the University Publication Centre (UPENA) of UiTM Pulau Pinang for having realised the publication of the sixth volume of the Esteem Academic Journal UiTM Pulau Pinang. In fact, it is the undivided support and all-round commitment from all those who were directly and indirectly involved in this project that was the pivotal factor for this success.

On behalf of UPENA UiTMPP, I would like to, first and foremost, express my sincerest gratitude to Associate Professor Mohd Zaki Abdullah, Director of UiTM Pulau Pinang, Associate Professor Dr Mohamad Abdullah Hemdi, Deputy Director of Academic Affairs and Associate Professor Ir. Damanhuri Jamalludin, Deputy Director of Research, Industry Linkages, Development & Maintenance for their unwavering support and being such a driving force towards this successful endeavour.

Not to be forgotten also is the service rendered by the distinguished panel of external reviewers for their constructive comments and criticisms in ensuring that the papers published in this issue would be of the highest quality. Similarly, the panel of language editors who had worked tirelessly towards ensuring that the papers published were linguistically perfect. To both these groups, UPENA is in awe of your efforts and salutes you!

UPENA is also impressed with the nature of papers submitted for publication. While this issue comprises all engineering based articles, it covers a wide array of sub-engineering disciplines. Kudos to these writers! UPENA sincerely appreciates their efforts and hopes more of our staff will follow in their footsteps.

Finally, research and publication are integral parts of an academic's life at any institution. Apart from being an institutional requirement, it is also essential for our own continuous self-development and knowledge expansion. To this effect, UPENA hopes to play a significant role by providing the platform upon which our staff can realise their dream. So, it is our hope at UPENA UITMPP that lecturers will take up the challenge and start to publish more vigorously from now on.

Rasaya Marimuthu Chief Editor ESTEEM Vol. 6, No. 1, 2010 (Engineering)

# VHDL and Computer Aided Design (CAD) Tool Teaching Aid for Future Engineers

Nor Fadzilah Mokhtar Afaf Rozan Mohd Radzol Nazirah Mohamat Kasim Noor Azila Ismail Faculty of Electrical Engineering Universiti Teknologi MARA (UiTM), Malaysia Email: norfadzilah105@ppinang.uitm.edu.my afafrozan944@ppinang.uitm.edu.my nazirah261@ppinang.uitm.edu.my noorazila687@ppinang.uitm.edu.my

Suzana Ab. Rahim Academy of Language Studies Universiti Teknologi MARA (UiTM), Malaysia Email: suzana.arahim@ppinang.uitm.edu.my

#### ABSTRACT

Recently, PLDs have replaced fixed function ICs in digital electronics application due to their advantages. VHDL is widely used in programming PLDs such as CPLD and FPGA among others. Introduction to VHDL, will give an advantage to future engineers for their career development. Since VHDL is a hardware description language, the teaching and learning process must be intuitive enough to help students to gain better understanding. Xilinx ISE software is one of the synthesizers available and used in the industry. An interactive and animated teaching aid has been developed to employ the advantages of e-learning pedagogy so as to optimize the teaching and learning process. This paper is to present the developed teaching aid and its interactive

ISSN 1675-7939

<sup>© 2010</sup> Universiti Teknologi MARA, Pulau Pinang and Universiti Teknologi MARA (UiTM), Malaysia.

Esteem Academic Journal

*features in assisting users in designing simple application of digital systems using VHDL (text entry) on PLDs platform.*

Keywords: e-learning, HDL, VHDL, Xilinx, FPGA, PLD

# Introduction

To cater to the needs of innovation and new technologies, the usage of fixed function IC has begun to be trimmed down in the production of consumer and industrial digital electronics application. Programmable Logic Devices (PLDs) such as FPGA, CPLD and others are now widely accepted and used in producing more compact, flexible, faster and cheaper products. Therefore, introducing software and hardware description language (HDL) used in programming the PLDs is a must for future engineers. Xilinx ISE software is one of the available Electronic Design Automation (EDA) tools in market, while very high speed integrated hardware description language (VHDL) is one of the popular HDLs used in programming PLDs.

# PLDs, VHDL and Xilinx ISE

Xilinx ISE offers text editor features to model digital systems using VHDL. Besides the text editor, it also offers schematic editor features to allow schematic entry design based. Xilinx ISE software usage will enhance future engineers' understanding in modeling the hardware using VHDL as it has features such as compiler/synthesizer and schematic viewer and simulator. The compiler/synthesizer is responsible for parsing the VHDL program, finding syntax errors, figuring out what the program really "says" and targeting the design to a specific hardware technology. The schematic viewer may create a schematic diagram corresponding to a VHDL program (Wakerly, 2007). The simulator is used to confirm the functionally by injecting stimulus to the design flow involved in programming a PLD.

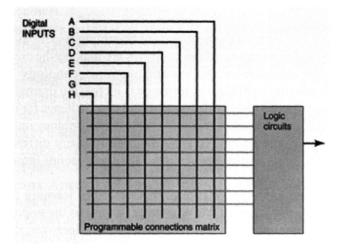

PLDs which contain the circuitry necessary to create logic functions are being used to implement digital systems. These devices are not programmed with a list of instruction, like a computer or digital signal processing (DSP). Instead, their internal hardware is configured by electronically connecting and disconnecting points in the circuit. Figure 1 generally depicts the internal architecture of a PLD. This PLD consists of some programmable connections. Each intersection between a row (horizontal wire) and a column (vertical wire) is a programmable connection. This connection can be programmed to be connected (1) or disconnected (0) (Tocci, Widmer & Moss, 2007).

Figure 1: PLD Architecture

There are many advantages of using PLDs. Among these are the lesser board space and power as well as the inventory usage. Apart from this, it lowers the manufacturing cost and heightens its reliability factor.

PLDs can be programmed using hardware description language (HDL). The role of HDL is to provide a concise and convenient way for the designer to describe the operation of the circuit in a format that a personal computer can handle and store data conveniently. The computer runs a special software application called compiler to translate from the HDL into the grid of 1s and 0s that can be loaded into the PLD. Programming PLD using HDL is much easier than trying to use Boolean Algebra, schematic drawing or truth table. However, like learning other languages, HDL needs to be used regularly to be mastered.

There are many HDLs developed by the manufacturers to program their PLDs such as AHDL, VHDL and Verilog. VHDL is a primary high-level hardware description language for designing and implementing digital circuit. The language has been standardized by the IEEE, making it appealing for engineers as well as makers of software tools that translate designs into the bit patterns used to program actual devices (Tocci et al., 2007).

# e-Learning

Computers and Internet connections are becoming widely available in university and classrooms. Many countries are making the creation and diffusion of information and communication technology (ICT) an important priority. In Malaysia, its usage is increasing dramatically. As ICT becomes more widely available, in would be a challenge for instructors to figure out how it would be best to integrate this technology into teaching and learning environments. ICT can be used in many different ways, and how it is integrated into educational settings depends largely on the instructors' instructional goals and strategies.

e-Learning is an umbrella term that describes learning done on a computer, usually connected to a network, giving us the opportunity to learn almost anytime, anywhere (Adibi, in press). Moreover, it is widely accepted that e-Learning can be as enriching and as valuable as the classroom experience or even more so. Not only that but e-Learning with its unique features, is an experience that leads to comprehension and mastery of new skills and knowledge, similar to its traditional counterpart.

Currently e-Learning has been accepted around the world as one of the education pedagogies due to its various advantages. Among the advantages of this respective learning are that it is self-paced, easily accessed, convenient and flexible. In addition, it lowers the cost of learning and provides global opportunities for the learners (Ning & Hong, 2010).

However, to ensure the effectiveness of e-Learning pedagogy, interactive e-Learning materials are a requisite in order to replace faceto-face classroom learning advantage. Currently there are many technologies available in market such as Adobe Captivate, Camtasia Studio, Flash and etc. which can be used to produce interactive materials.

### Methodology

Adobe Captivate 4 is used to develop the user manual since it offers several features to produce an interactive material to introduce Xilinx ISE environment in programming the PLD. It is screen captured software which is extremely useful for educators to introduce new technology to the new learners.

The software is installed from CD or downloaded from Adobe website. It has several features to record activities such as using software applications, moving between applications, visiting or accessing websites or making system configurations.

Before starting the recording process, the material of the teaching aid is planned and prepared. For this project, power point notes included in the form of a screen capture project is converted into a flash (.swf) file. The features of Xilinx software and VHDL code need to be determined before the process of capturing the application activities actually starts. After completing the material, the process of capturing the screen activities is done and the captured screen desktops are eventually saved as slides or video files. This teaching aid consists of several examples of different VHDL coding styles. As a result, several different slides are required to be captured to complete the project.

After the initial screen capture is completed, the process of editing proceeds. The screen recording applications have the options to add titles, highlight specific area of the screen, insert callouts, alter the mouse movement, add new captions, insert audio, set a playback window and control and specify how they are to be sequenced (Paul Daniels & Bateson, 2009).

Finally, all of the edited captured screen slides are assembled into one screen that consists of menu, captured screen window, playback window and control using aggregator project application in Adobe Captivate software.

#### Results

#### VHDL and CAD Tool Teaching Aid

VHDL and Computer Aided Design (CAD) tool Teaching Aid is developed to exploit some of the e-Learning advantages. Using this

teaching aid, users are able to learn according to their own pace and this will give students a chance to speed up or slow down as necessary. Besides, the ongoing availability feature allows the users to choose the most suitable time to learn and utilize the software.

The following section will highlight the teaching aid that has been developed to aid the teaching and learning of VHDL. The front page of the product is shown in Figure 2.

Figure 2: Front Page

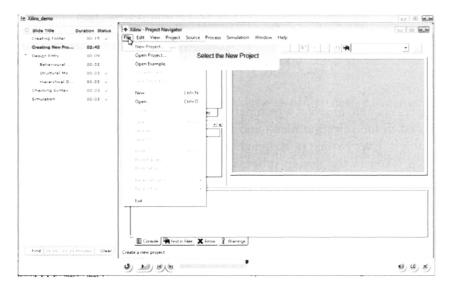

The window is divided into three parts which are "selection menu", "captured movie workspace" and "audio-visual control panel" as shown in Figure 3.

| the 104 kill familing did for \$70144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1+ Xite - Frijed Nacijsta                     |   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|---|

| m parana masara tahun karan<br>Mulan karana tahun karan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 이번 189 Yee Papel Love Press Sector State Page | • |

| State Type         Burden Baue           Scholl Prop.         Scholl Prop.           Prosting, How and, 1         Scholl Prop.           Scholl Prop.         Scholl Prop.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                               |   |

| er (1, 3, 4, 4, 2)<br>Kapper (2, 2)<br>K |                                               |   |

| SELECTION<br>MENU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                               |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                               |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | AUDIO-VISUAL CONTROL PANEL                    |   |

Figure 3: Interactive Animated Window

Captured movie workspace displays the captured screens of Xilinx ISE design workspace. As the movie plays, there will be pop - up dialogs as shown in Figure 4 to further help the users in practising the design procedure.

Figure 4: Window with Pop Up Dialog

The selection menu shown in Figure 5 lists all the videos available.

| 0 | Slide Title        | Duration | Status  |

|---|--------------------|----------|---------|

| 0 | Cover Page         | 00:20    | ~       |

| 0 | VHDL Notes         | 02:15    | 11.7.5- |

| 0 | Design Flow        | 00:36    |         |

| 0 | Creating Folder    | 00:52    |         |

| 0 | Creating New Pro   | 02:04    |         |

| 0 | Data Flow Entry    | 05:42    |         |

| 0 | With Select Whe    | 06:39    |         |

| 0 | When Else Entry    | 03:57    |         |

| 0 | If Else Stat Entry | 05:57    |         |

| 0 | Case When Entry    | 05:10    |         |

| 0 | Top Layer Demo     | 04:01    |         |

| 0 | Bottom Layer De    | 01:51    |         |

|   |                    |          |         |

Figure 5: Selection Menu

Users are able to select which particular part they need to view. Videos listed in the selection menu and their descriptions are summarized in Table 1. Every video is designed to have audio effect, explaining every step taken in the design process. There are two methods of VHDL modelling introduced in the teaching aid. The methods are "Behavioral modeling and "Structural modeling".

| Menu                      | Description                                                                                                                                                          |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cover Page                | An introduction page showing the designers' name with audio effect introducing the software                                                                          |

| VHDL Notes                | Contains theoretical notes on VHDL. The same notes are used in<br>the lecture. The student can view the videos to refresh the knowledge<br>covered in lecture.       |

| Creating Folder           | Shows the student how to create a new folder. This video emphasizes<br>on the importance of placing the developed programme accordingly<br>to avoid being misplaced. |

| Creating New<br>Project   | Shows the initial stages of starting a new project.                                                                                                                  |

| Data Flow Entry           | Contains an example of VHDL programming using Behavioral modelling: Data Flow design entry                                                                           |

| Select With<br>When Entry | Contains an example of VHDL programming using Behavioral modelling: Select With When design entry                                                                    |

| When Else Entry           | Contains an example of VHDL programming using Behavioral modelling: When Else Entry design entry                                                                     |

| If Else State<br>Entry    | Contains an example of VHDL programming using Behavioral modelling: If Else State Entry design entry                                                                 |

| Case When Entry           | Contains an example of VHDL programming using Behavioral modelling: Case When Entry design entry                                                                     |

| Top Layer                 | Contains an example how to create a top layer programming for a structural modeling                                                                                  |

| Bottom Layer              | Contains an example how to create a bottom layer programming for a structural modeling                                                                               |

Table 1: Description on Videos Listed in the Selection Menu

In behavioral modeling method, examples of five design statements are shown. They are "data flow", "with select when", "when else", "if else" and "case when".

Each design entry statement example is a video showing all the required steps in design procedure starting from design entry, synthesis and simulation. Meanwhile, for structural modeling method, the last two videos show examples on how to create a top level and bottom level programming.

Basic theoretical notes on VHDL are also included to assist the user in designing digital electronics application using VHDL as shown in Figure 6. Besides, common syntax errors are also shown to help the user in troubleshooting their programme respectively.

| Xilinx ISE Teaching Aid for EP0242 St<br>Nor Fadzilah & Afaf Rozan<br>EP0242 Lecturers<br>norfadzilah105@ppinang.uitm.edu.my | Design Entry Method                                                                                            |  |

|------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--|

| G Slide Title Duration Status                                                                                                |                                                                                                                |  |

| Introduction 00:18 🗸                                                                                                         |                                                                                                                |  |

| Step1 - Creating 00:52 🗸                                                                                                     | <ul> <li>Design descriptions can be either or a combination</li> </ul>                                         |  |

| Step2 - Creating 02:04 🖌                                                                                                     | of                                                                                                             |  |

| Step3 · Design e 00:03 🖌                                                                                                     | Structural                                                                                                     |  |

| Data Flo 03:14                                                                                                               | – Structural                                                                                                   |  |

| with Sel 03:32                                                                                                               | <ul> <li>Instantiations (placements of logic-much like in a</li> </ul>                                         |  |

| When EL. 03:57                                                                                                               | schematic and their connections) of building blocks                                                            |  |

| If Else E 02:58<br>Care W 05:10                                                                                              | referred to as components                                                                                      |  |

| Hireacht 00:06                                                                                                               | Example - port map                                                                                             |  |

| Top 04:01                                                                                                                    |                                                                                                                |  |

| 8 ott. 01:51                                                                                                                 | – Behavioral                                                                                                   |  |

| Step4 - Checking 00:54                                                                                                       | <ul> <li>Describe the behavior of the system with an algorithm</li> </ul>                                      |  |

| Step5 - Simulate 02:55                                                                                                       | , ,                                                                                                            |  |

| Simulati . 02:48                                                                                                             | <ul> <li>Example – Case when statement, if else statement</li> </ul>                                           |  |

|                                                                                                                              | – Dataflow                                                                                                     |  |

|                                                                                                                              | <ul> <li>Define the relation between input / output signals with<br/>simple logic operation (&lt;=)</li> </ul> |  |

| 03:17/34:49 Minutes 67 Clear                                                                                                 |                                                                                                                |  |

|                                                                                                                              | 21 /2 /2 www.www.www.www.www.www.www.www.www.ww                                                                |  |

Figure 6: VHDL Notes

Audio-visual control panel as shown in Figure 7 consists of the rewind, pause/play, back, forward, video progress bar, on-off audio and close caption (CC) buttons. The On-off audio button is to enable/ disable the audio feature and CC button is to enable/ disable caption feature. The Caption feature displays the text version of the audio. The indicator on the progress bar can be moved to rewind and forward the video.

Figure 7: Audio-visual Control Panel

## Conclusion

The interactive teaching aid is developed to benefit the beginners of Xilinx ISE software and VHDL. The contents are intended as an introduction level for the new users. To further help these new users, theoretical notes are also included. Furthermore, common syntax errors are also discussed. The most important feature of this teaching aid is the interactive and animated environment it offers. This is to ensure that users find it very helpful even without the instructor's help. The animated visuals help users in using the software in a short time span compared to reading the help file alone. The selection menu and audio-visual control panel features allow users to do self-revision and as such, this helps optimize their learning process. On the whole, the developed teaching aid is expected to optimize the learning process for the new users and they could also gain the many benefits of e-learning.

# References

- Adibi, S. (in press). A remote interactive non-repudiation multimediabased m-learning system. *Telematics and Informatics*.

- Ning, Z., & Hong, B. (Jan. 2010). Research on Computer Technology for E-learning in Higher Education. Paper presented at the International Conference on e-Education, e-Business, e-Management, and e-Learning, IC4E '10.

- Paul Daniels, & Bateson, G. (2009). Technically speaking: Screen recording software for creating instructional material. *Jalt Call Journal*, 5(2), 84-92.

- Tocci, R. J., Widmer, N. S., & Moss, G. L. (2007). *Digital Systems Principles and Applications* (10<sup>th</sup> ed.). New Jersey: Pearson Prentice Hall.

- Wakerly, J. F. (2007). *Digital Design Principles and Practices* (4<sup>th</sup> ed.). New Jersey: Pearson Prentice Hall.